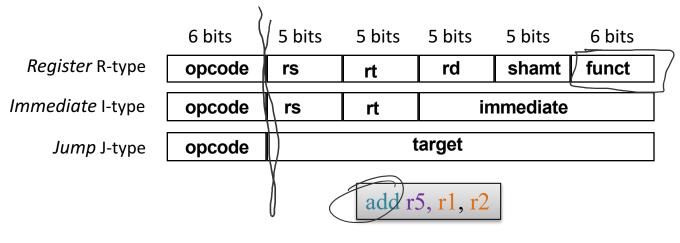

#### Example of instruction encoding:

0000000001000100010100000100000

0x00222420

### Poll Q: Implications of the MIPS instruction format

What is the maximum number of unique operations MIP\$ can encode?

3

6 64

127

128

## Accessing the Operands aka, what's allowed to go here

- operands are generally in one of two places:

- registers (32) options)

- memory (2<sup>32</sup>/locations)

- registers are

- easy to specify

- close to the processor (fast access)

- the idea that we want to use registers whenever possible led to *load-store architectures*.

- normal arithmetic instructions only access registers

- only access memory with explicit loads and stores

#### Poll Q: Accessing the Operands

There are typically two locations for operands: registers (internal storage - \$t0, \$a0) and memory. In each column we have which (reg or mem) is better.

#### Which row is correct?

|   | E | Faster access   | Fewer bits to specify | More locations |

|---|---|-----------------|-----------------------|----------------|

|   | Α | Mem             | Mem                   | Reg            |

| 5 | B | Mem             | Reg                   | Mem            |

|   | C | Reg             | Mem                   | Reg            |

|   | D | Reg             | Reg                   | Mem            |

|   | E | None of the abo | ove                   |                |

#### MIPS uses a load/store architecture to access operands

can do: can't do add

$$$t0 = $s1 + $s2$$

and  $[w $t0, 32($s3)]$

- → forces heavy dependence on registers, which is exactly what you want in today's CPUs

- more instructions

- + fast implementation (e.g., easy pipelining)

What pushes MIPS towards a load/store design? (hint: fixed instruction length)

#### **How Many Operands?**

aka how many of these?

- Most instructions have three operands (e.g.,  $\sqrt{z} = x + y$ ).

- Well-known ISAs specify 0-3 (explicit) operands per instruction.

- Operands can be specified mplicitly or explicity.

Historically, many classes of ISAs have been explored, and trade off compactness, performance, and complexity

| Style                      | # Operands | Example                                   | <b>Operation</b>                                                                                                                            |

|----------------------------|------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Stack                      | 0          | add                                       | $tos_{(N-1)} \leftarrow tos_{(N)} + tos_{(N-1)}$                                                                                            |

| Accumulator                | 1          | add A                                     | $acc \leftarrow acc + mem[A]$                                                                                                               |

| General Purpos<br>Register | se 3       | add A B Rc<br>add A Rc                    | $\underline{\text{mem[A]}} \leftarrow \underline{\text{mem[B]}} + Rc$ $\underline{\text{mem[A]}} \leftarrow \underline{\text{mem[A]}} + Rc$ |

| Load/Store:                | <u></u>    | Jadd Ra Rb Rc<br>load Ra Rb<br>store Ra A | $Ra \leftarrow Rb + Rc$ $Ra \leftarrow mem[Rb]$ $mem[A] \leftarrow Ra$                                                                      |

| Stack | Stack | <u>Accumulator</u> | <u>GP Register</u> | GP Register |  |

|-------|-------|--------------------|--------------------|-------------|--|

|       |       | (register-memory)  | (load-store)       |             |  |

| <u>Stack</u> | <u>Accumulator</u> | <u>GP Register</u> | <u>GP Register</u> |

|--------------|--------------------|--------------------|--------------------|

|              |                    | (register-memory)  | (load-store)       |

| _ Push A     |                    |                    |                    |

| ~ Push B     |                    |                    |                    |

| —Add         |                    |                    |                    |

| -Pop C       |                    |                    |                    |

| <u>Stack</u> | <u>Accumulator</u> | GP Register       | GP Register  |

|--------------|--------------------|-------------------|--------------|

|              |                    | (register-memory) | (load-store) |

| Push A       | Load A             |                   |              |

| Push B       | Add B              |                   |              |

| Add          | Store C            |                   |              |

| Pop C        |                    |                   |              |

| <u>Stack</u> | <u>Accumulator</u> | <u>GP Register</u> | <u>GP Register</u> |

|--------------|--------------------|--------------------|--------------------|

|              |                    | (register-memory)  | (load-store)       |

| Push A       | Load A             | ADD C, A, B        |                    |

| Push B       | Add B              | 1 ) >              |                    |

| Add          | Store C            | L 232 232          |                    |

| Pop C        |                    |                    |                    |

| Stack  | <u>Accumulator</u> | GP Register       | GP Register    |

|--------|--------------------|-------------------|----------------|

|        |                    | (register-memory) | (load-store)   |

| Push A | Load A             | ADD C, A, B       | _ Load R1,A    |

| Push B | Add B              |                   | ~ Load R2,B    |

| Add    | Store C            |                   | ^ Add R3,R1,R2 |

| Pop C  |                    |                   | - Store C,R3   |

|        |                    |                   |                |

## Exercise: Working through alternative ISAs

[if time]

A = X\*Y - B\*C

Stack Architecture Accumulator

GPR

GPR (Load-store)

| A a ayymyylatan | Stack |      | Memory |

|-----------------|-------|------|--------|

| Accumulator     |       | A    |        |

|                 |       | X    | 12     |

| R1              |       | Y    | 3      |

| R2              |       | В    | 4      |

|                 |       | C    | 5      |

| R3              |       | temp |        |

## Poll Q: The destination of a MIPS add operation can be...

- Only the top of the stack

Only the accumulator register

- Any general purpose register,

- Any general purpose register or anywhere in me

- Any general purpose register or the top of the stack

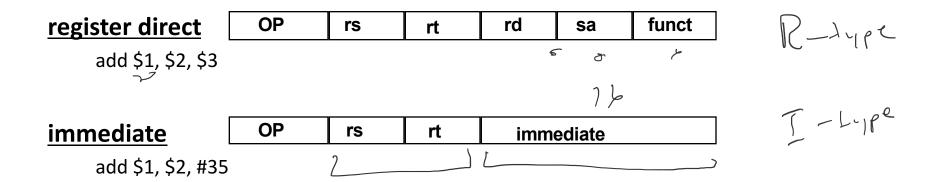

# Addressing Modes aka: how do we specify the operand we want?

- Register direct

- Immediate (literal)

- Direct (absolute)

- Register indirect

- Base+Displacement

- → Base+Index

- Scaled Index

- Autoincrement

- Autodecrement

- Memory Indirect

M[ M[R3] ]

strut?

all 1, 12, \$10

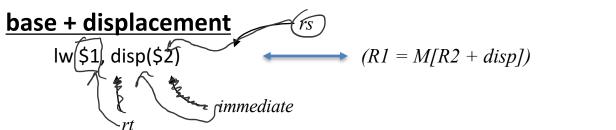

#### MIPS addressing modes and syntax

register indirect

$$\Rightarrow disp = 0$$

absolute

$$\Rightarrow (rs) = 0$$

#### Is this sufficient?

- measurements on the VAX show that these addressing modes (immediate, direct, register indirect, and base+displacement) represent 88% of all addressing mode usage.

- similar measurements show that 16 bits is enough for the immediate 75 to 80% of the time

- and that 16 bits is enough of a displacement 99% of the time.

- (and when these are not sufficient, it typically means we need one more instruction)

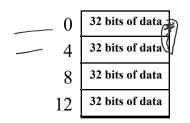

#### What does memory look like anyway?

- Viewed as a large, single-dimension array, with an address.

- A memory address is an index into the array

- "Byte addressing" means that the index (address) points to a byte of memory.

| 0 | 8 bits of data |

|---|----------------|

| 1 | 8 bits of data |

| 2 | 8 bits of data |

| 3 | 8 bits of data |

| 4 | 8 bits of data |

| 5 | 8 bits of data |

| 6 | 8 bits of data |

...

# Memory accesses are (often) required to be "word-aligned" because of how buses and memory work

- Bytes are nice, but most data items use larger "words"

- For MIPS, a word is 32 bits or 4 bytes.

i.e., what are the least 2 significant bits of a word address?

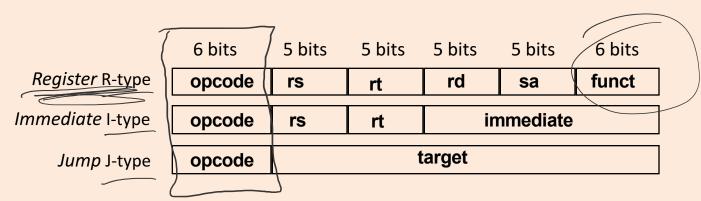

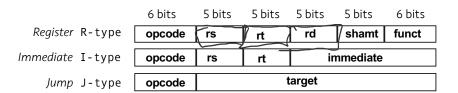

#### The MIPS ISA, so far

- fixed 32-bit instructions

- × 3 instruction formats (R, I, J)

- ✓ 3-operand, load-store architecture

- <sup>1</sup> 32 general-purpose registers

- R0 always equals 0.

- 2 additional special-purpose integer registers, HI and LO, because multiply and divide produce more than 32 bits.

- registers are 32-bits wide (word)

- register, immediate, and base+displacement addressing modes

### But what kinds of things do computers actually do?

- arithmetic

- logical

- data transfer

- conditional branch

- unconditional jump

## Which kinds of instructions does (and doesn't) the MIPS ISA support?

- arithmetic

- add, subtract, multiply, divide

- But not: Start, Mors, SIN COS, ADC

- logical

- and, or, shift left, shift right  $_1 \times \infty$

- But not: BIL &= > &= \ (m)

- data transfer

- load word, store word

1) == brah 3

#### "Control Flow" describes how programs execute

- Jumps

- Procedure call (jump subroutine)

- Conditional Branch

- Used to implement, for example, if-then-else logic, loops, etc.

- Control flow must specify two things

- Condition under which the jump or branch is taken

- If take, the location to read the next instruction from ("target")