#### **CSE 141: Introduction to Computer Architecture**

**Pipelines**

### First things first: *Pipelines are the coolest.*

• Seriously, this idea is everywhere

Een. Affing

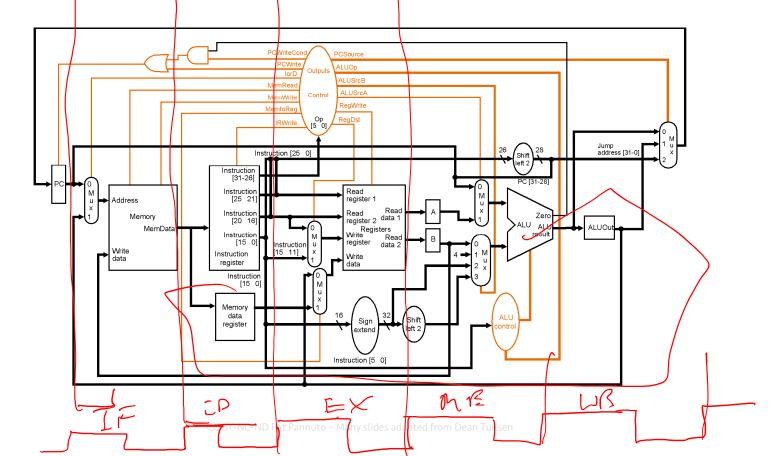

CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen

### THE key idea of pipelining

- Throughput >>> latency

- Computers are very useful because they do <u>a lot</u> of things well

- It is much less important how well any one thing is done

- Which is faster?

- A machine with average CPI of 2.0 running at 48 MHz

LET

- A machine with average CPI of 10.0 running at 4 GHz

FINST

Instruction [5-0]

extend

ALU ontro

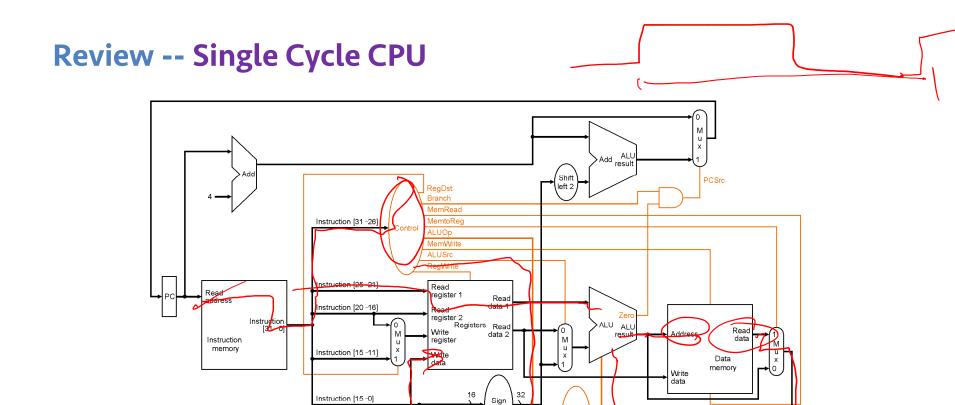

# (not quite) Review -- Multiple Cycle CPU

CSE 141

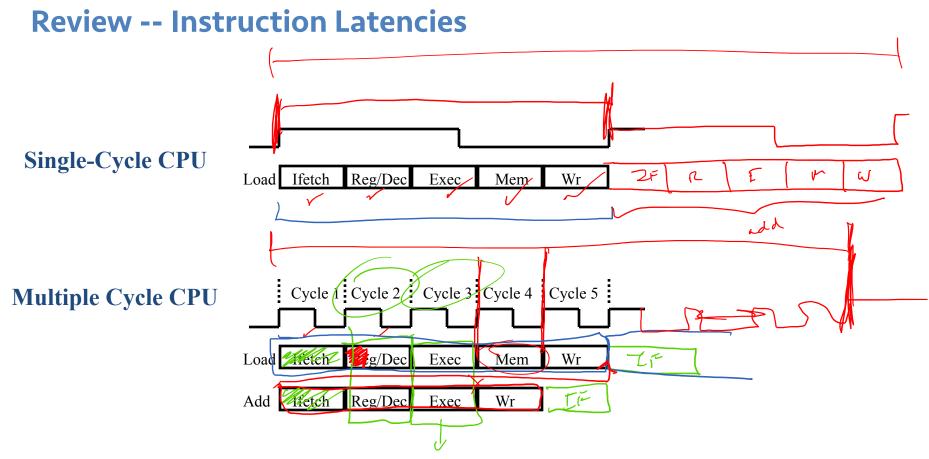

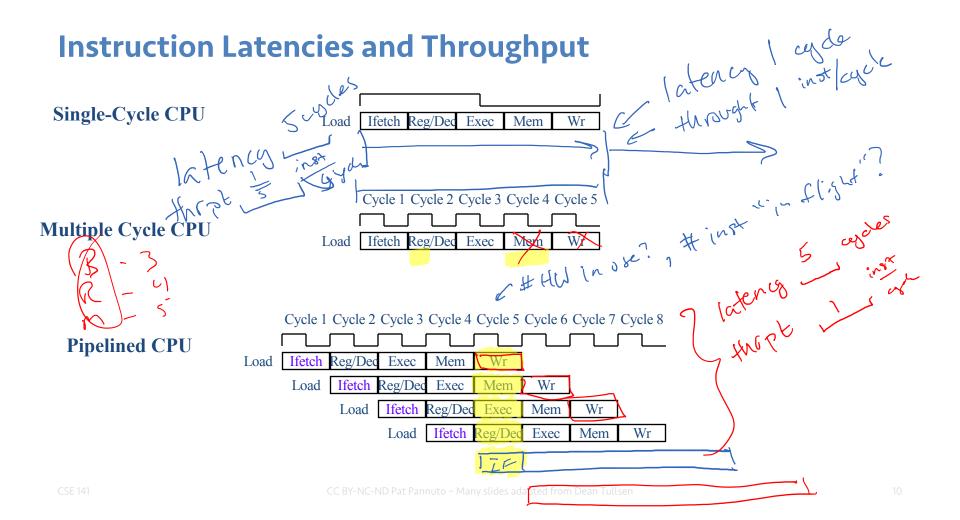

#### Instruction Latencies and Throughput

Single-Cycle CPU

Multiple Cycle CPU

| Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 |        |         |      |     | Cycle 5 |

|-----------------------------------------|--------|---------|------|-----|---------|

|                                         |        |         |      |     |         |

| Load                                    | Ifetch | Reg/Dec | Exec | Mem | Wr      |

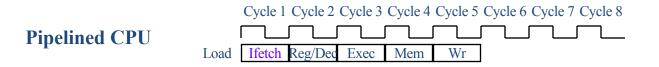

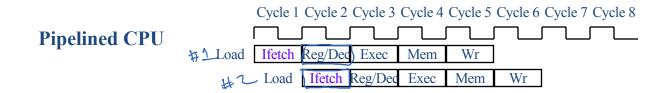

**Pipelined CPU**

#### Instruction Latencies and Throughput

**Single-Cycle CPU**

Multiple Cycle CPU

|      | Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 |         |      |     |    |

|------|-----------------------------------------|---------|------|-----|----|

|      |                                         |         |      |     |    |

| Load | Ifetch                                  | Reg/Dec | Exec | Mem | Wr |

#### Instruction Latencies and Throughput

**Single-Cycle CPU**

Multiple Cycle CPU

|      | Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 |         |      |     |    |

|------|-----------------------------------------|---------|------|-----|----|

|      |                                         |         |      |     |    |

| Load | Ifetch                                  | Reg/Dec | Exec | Mem | Wr |

### **Pipelining Advantages**

- Higher *maximum* throughput

- Higher *utilization* of CPU resources

- But, more complicated *datapath*, more complex control(?)

## Poll Q: What affects throughput? Peak throughput depends on...

|            | Single Cycle        | Multi-Cycle         | Pipeline            |

|------------|---------------------|---------------------|---------------------|

|            | Longest Instruction | Cycle Time          | Average Instruction |

| B          | Longest Instruction | Cycle Time          | Longest Instruction |

| $\bigcirc$ | Longest Instruction | Average Instruction | Cycle Time          |

| D          | Average Instruction | Longest Instruction | Cycle Time          |

| Е          | None of the above   |                     |                     |