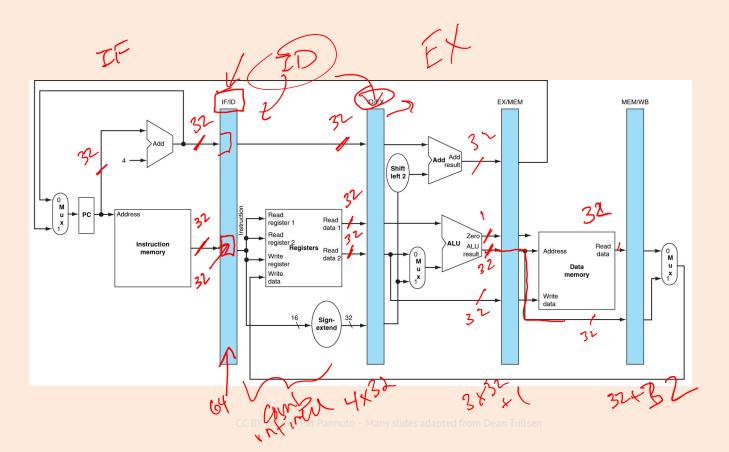

# Poll Q: How many D flip flops are in this pipeline?

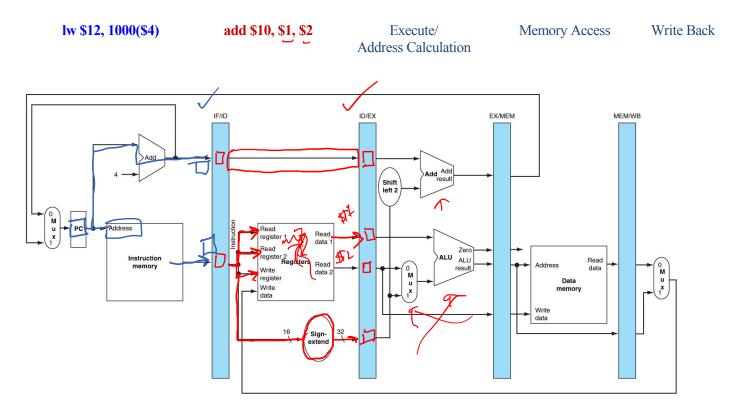

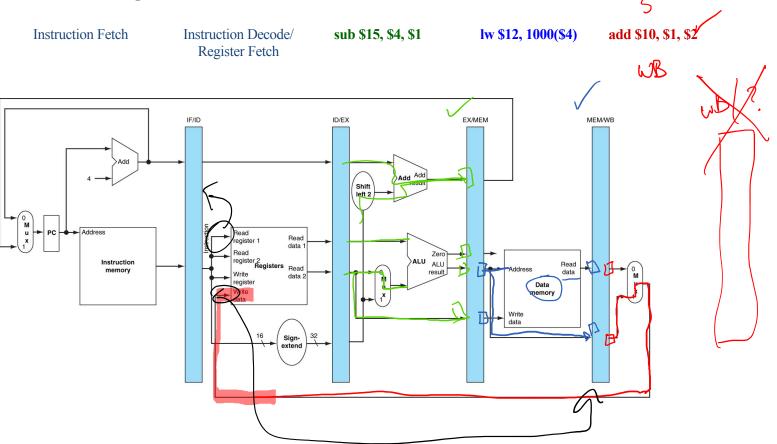

add \$10, \$1, \$2 Instruction

Instruction Decode/ Register Fetch Execute/ Address Calculation Memory Access

Write Back

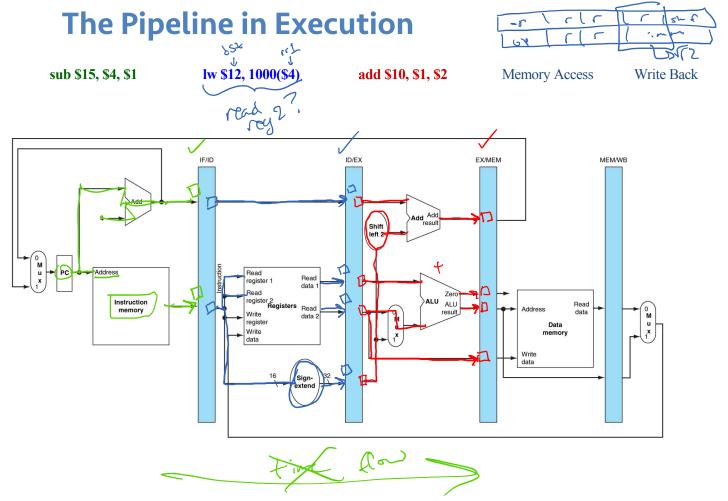

#### The Pipeline in Execution add \$10, \$1, \$2 Instruction Fetch sub \$15, \$4, \$1 lw \$12, 1000(\$4) Write Back EX/MEM MEM/WB PC Address Read register 1 register 2 Registers Read Instruction Read data Write

( (bluser)

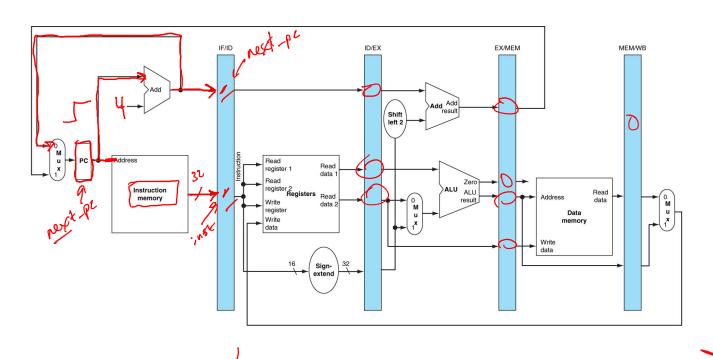

Instruction Fetch

Instruction Decode/ Register Fetch Execute/ Address Calculation sub \$15, \$4, \$1

lw \$12, 1000(\$4)

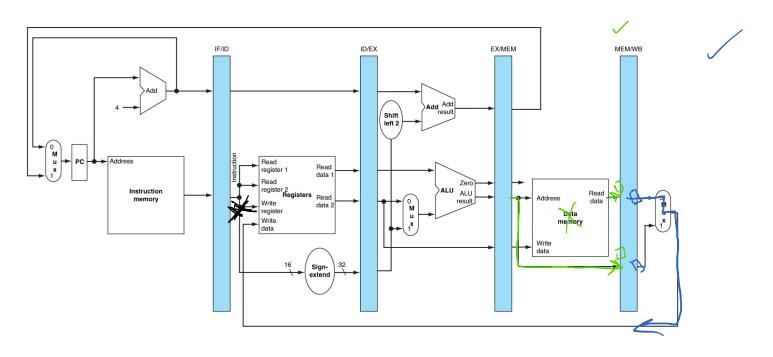

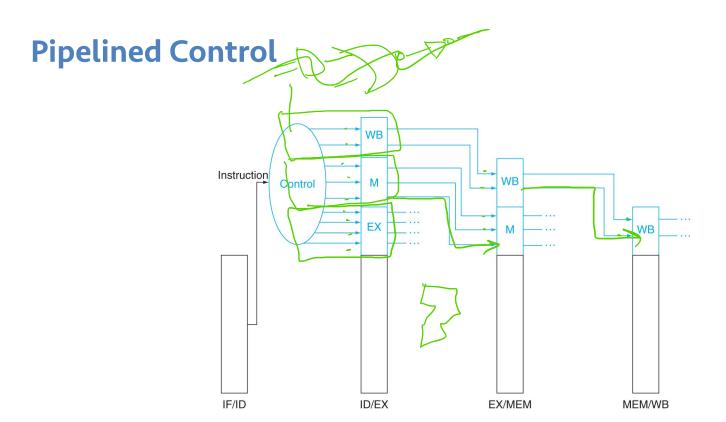

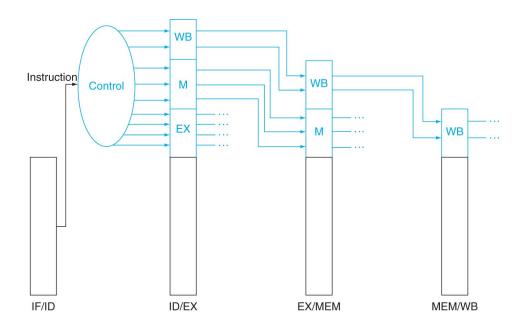

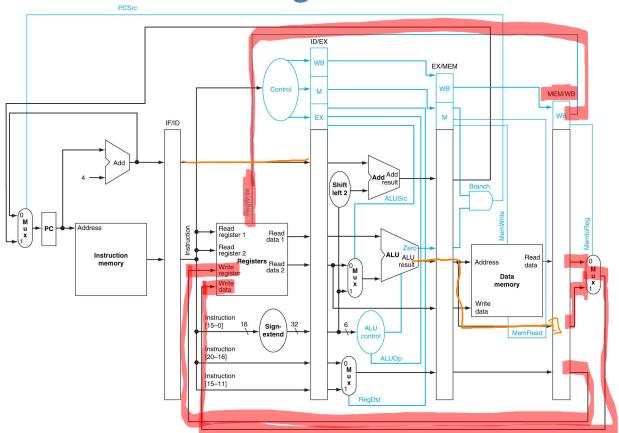

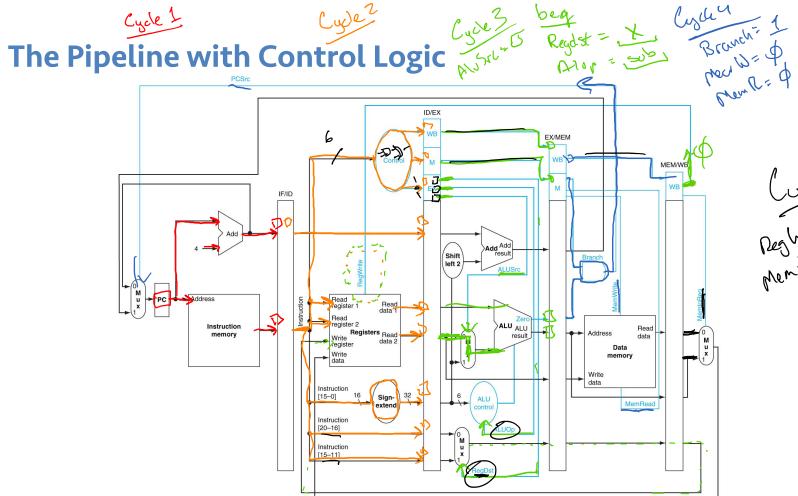

### The Pipeline, with controls But....

I told you multicycle control was messy. We would expect pipelined control to be messier.

- I told you multicycle control was messy. We would expect pipelined control to be messier.

- Why?

- I told you multicycle control was messy. We would expect pipelined control to be messier.

- Why?

- But it turns out we can do it with just...

- I told you multicycle control was messy. We would expect pipelined control to be messier.

- Why?

- But it turns out we can do it with just...

- Combinational logic!

- Signals generated once

- Follow instruction through the pipeline

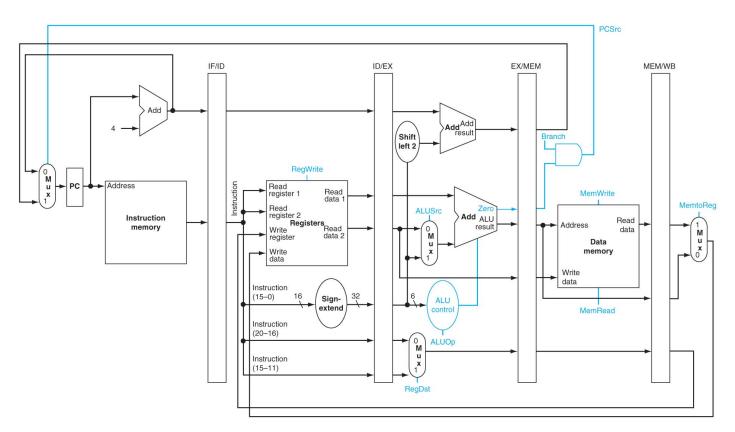

# Recall: Control signals in the single-cycle machine

So, really it is combinational logic and some registers to propagate the signals to the right stage.

# The Pipeline with Control Logic

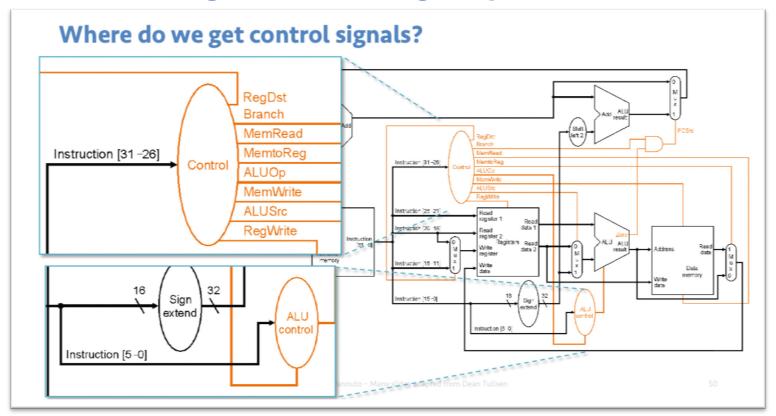

# **Pipelined Control Signals**

|             | Execution Stage Control Lines |        |        |        | Memory Stage Control Lines |         |          | Write Back Stage Control |          |

|-------------|-------------------------------|--------|--------|--------|----------------------------|---------|----------|--------------------------|----------|

|             |                               |        |        |        |                            |         |          | Lines                    |          |

| Instruction | RegDst                        | ALUOp1 | ALUOp0 | ALUSrc | Branch                     | MemRead | MemWrite | RegWrite                 | MemtoReg |

| R-Format    | 1                             | 1      | 0      | 0      | 0                          | 0       | 0        | 1                        | 0        |

| lw          | 0                             | 0      | 0      | 1      | 0                          | 1       | 0        | 1                        | 1        |

| sw          | X                             | 0      | 0      | 1      | 0                          | 0       | 1        | 0                        | X        |

| beq         | X                             | 0      | 1      | 0      | 1                          | 0       | 0        | 0                        | X        |

# **Pipelined Control Signals**

|             | Execution Stage Control Lines |        |        |        | Memory Stage Control Lines |         |          | Write Back Stage Control<br>Lines |          |

|-------------|-------------------------------|--------|--------|--------|----------------------------|---------|----------|-----------------------------------|----------|

| Instruction | RegDst                        | ALUOp1 | ALUOp0 | ALUSrc | Branch                     | MemRead | MemWrite | RegWrite                          | MemtoReg |

| R-Format    | 1                             | 1      | 0      | 0      | 0                          | 0       | 0        | 1                                 | 0        |

| lw          | 0                             | 0      | 0      | 1      | 0                          | 1       | 0        | 1                                 | 1        |

| SW          | X                             | 0      | 0      | 1      | 0                          | 0       | 1        | 0                                 | X        |

| beq         | X                             | 0      | 1      | 0      | 1                          | 0       | 0        | 0                                 | X        |

Let's just do one.

Republes - X

## Is it really that easy?

What happens when...

```

add $3, $10, $11

lw $8, 1000($3)

sub $11, $8, $7

```