### Announcements

- Reminder: Clocks change on Sunday

- You get 2am twice!

- Midterm logistics

- Following the path-of-most-success from other faculty

- Will be on canvas

- Will be timed

- Will allow forward progress only

- N.b. This is how many standardized tests you will encounter (e.g. GRE) work

- We will give you, in advance, a list of questions and suggested timing

- Will not use the (IMHO creepy) remote proctoring, etc services

- Open book, not open Google [but you will not have time to look everything up!]

- The participation quizzes will be configured this way so you can get comfortable

- Only difference is participation quizzes will let you see correct answers when you're done

# A brief aside: CSE 141 in the real world

• Literally, in the hour before lecture, during the TockOS project call...

**Q8**. The PowerPC ISA supports the load\_indexed instruction, as in load\_indexed \$rd, \$rs, \$rt which means R[\$rd] = M[\$rs+\$rt]. In what ways would we need to change the processor (e.g., Fig 4.15, P&H) to support that instruction? Just consider the datapath, not control logic, and describe the changes.

RISC-V does not support

a branch\_indexed instruction,

which makes switch/case

expensive in code size, which

may change how our OS works

We've settled on syscalling and what return types look like and are now looking at the generated assembly. We've done a few tweaks to try to trim it down. He's doing Cortex-M and I'm doing RISC-V. Here's what syscalling looks like:

https://github.com/tock/tock/blob/tock-2.0-dev/kernel/src/syscall.rs

The major issue I'm seeing in RISC-V is not great support for switch/case tables. This, for example, is some of the generate assembly of encode\_system\_return, which serializes the Rust enum for the return type into registers. The key thing here are 0x5680 to 0x560:1 guess there is no table mechanism (unlike tibb in ARM), so it just a series of If-elses. This suggests that we might want to think about the ordering of values so common cases are early.

|   | 2000589c _ZN6kernel7sysc | il25GenericSyscallReturnValue21encode_syscall_return17h7fa68817240ce495 |

|---|--------------------------|-------------------------------------------------------------------------|

|   | 2000589c: 83 28 05 00    | lw a7, 0(a0)                                                            |

|   | 200058a0: 63 82 08 04    | beqz a7, 68                                                             |

|   | 200058a4: 05 48          | addi a6, zero, 1                                                        |

|   | 200058a6: 63 83 08 05    | beq a7, a6, 70                                                          |

|   | 200058aa: 09 48          | addi a6, zero, 2                                                        |

|   | 200058ac: 63 85 08 05    | beq a7, a6, 74                                                          |

|   | 200058b0: 0d 48          | addi a6, zero, 3                                                        |

|   | 200058b2: 63 8c 08 05    | beq a7, a6, 88                                                          |

|   | 200058b6: 91 47          | addi a5, zero, 4                                                        |

|   | 200058b8: 63 84 f8 06    | beq a7, a5, 104                                                         |

|   | 200058bc: 95 47          | addi a5, zero, 5                                                        |

|   | 200058be: 63 85 f8 06    | beq a7, a5, 106                                                         |

|   | 200058c2: 99 47          | addi a5, zero, 6                                                        |

|   | 200058c4: 63 8b f8 08    | beq a7, a5, 150                                                         |

|   | 200058c8: 9d 47          | addi a5, zero, 7                                                        |

|   | 200058ca: 63 85 f8 06    | beq a7, a5, 106                                                         |

|   | 200058ce: a1 47          | addi a5, zero, 8                                                        |

| 1 | 200058d0: 63 80 f8 08    | beq a7, a5, 128                                                         |

|   | 200058d4: 03 28 c5 00    | lw a6, 12(a0)                                                           |

|   | 200058d8: 1c 45          | lw a5, 8(a0)                                                            |

|   | 200058da: 83 28 45 00    | lw a7, 4(a0)                                                            |

# Is it really that easy?

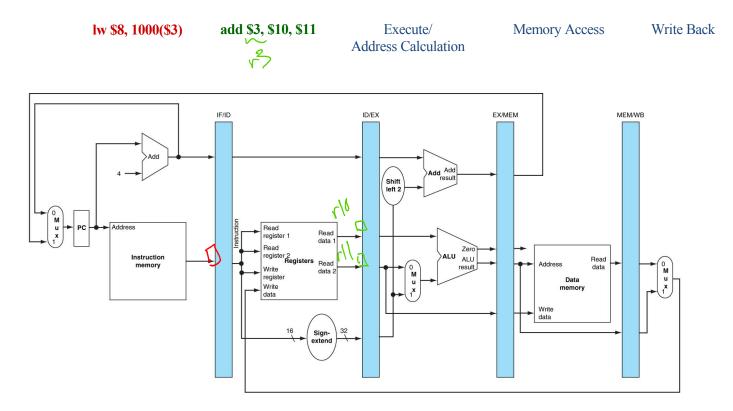

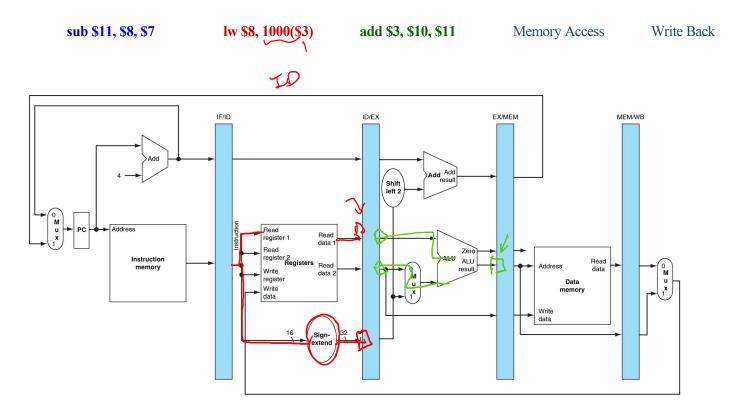

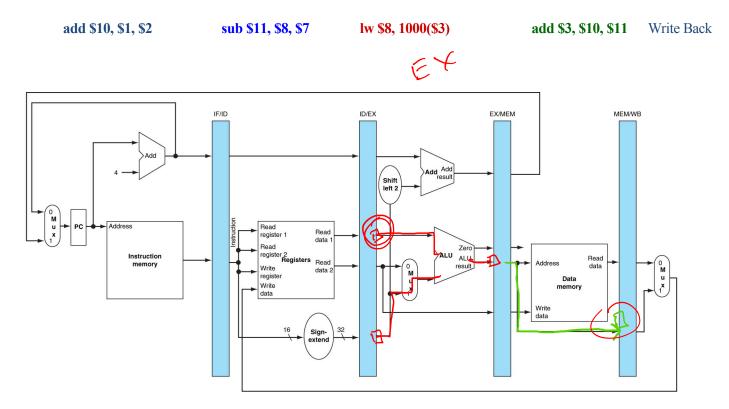

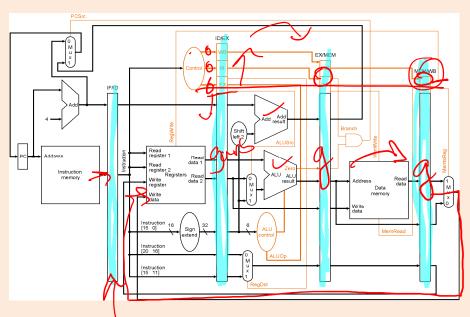

What happens when... add \$3, \$10, \$11

lw \$8, 1000(\$3)

sub \$11, \$8, \$7

## **The Pipeline in Execution**

## **The Pipeline in Execution**

## **The Pipeline in Execution**

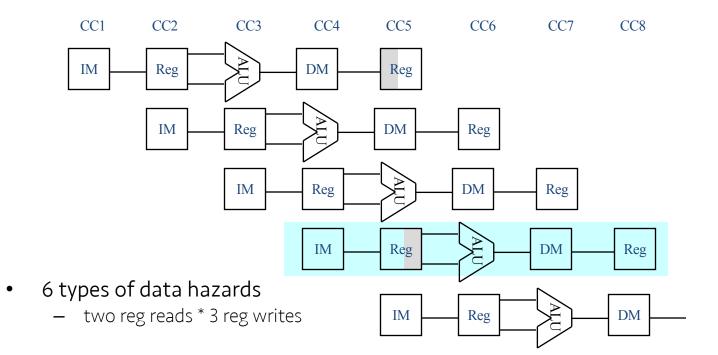

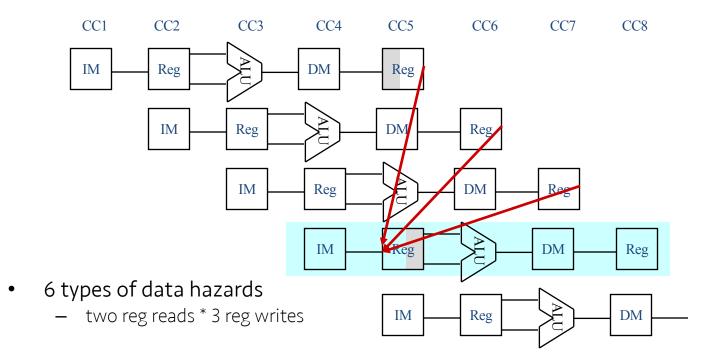

### **Data Hazards**

When a result is needed in the pipeline before it is available, a **data hazard** occurs. *What can we do?*

### **Data Hazards**

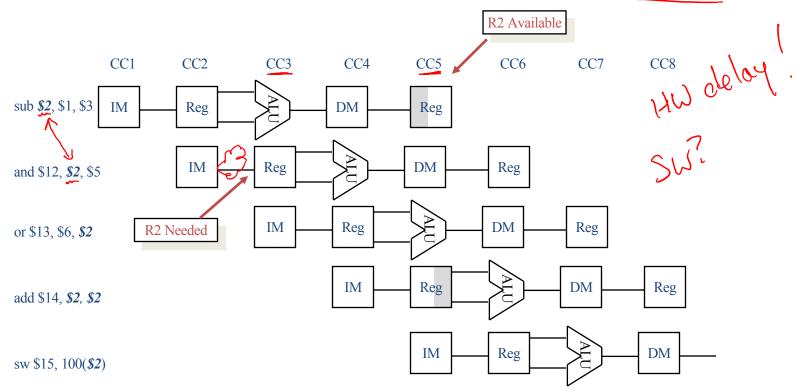

- Data Hazards are caused by data dependences

- Not all data dependences result in data hazards

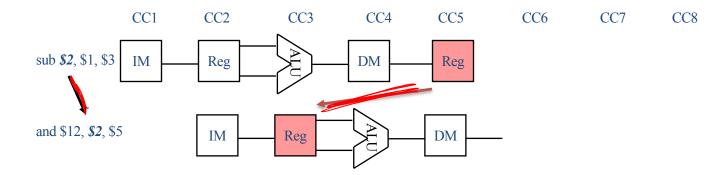

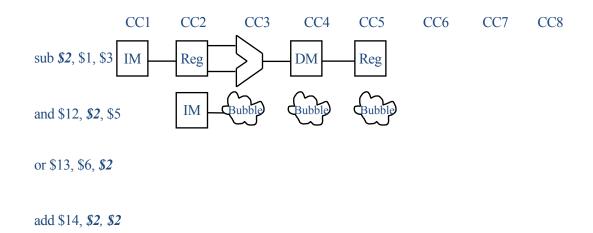

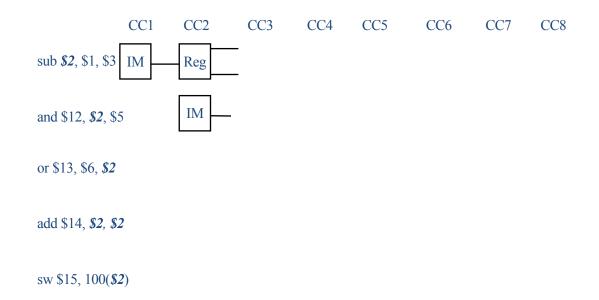

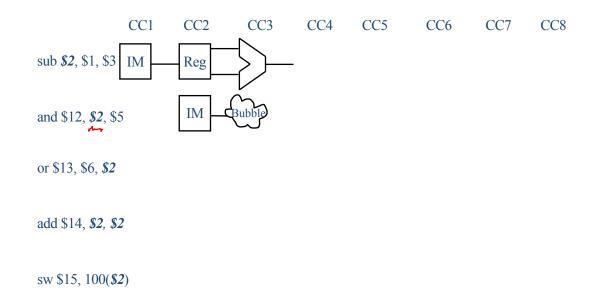

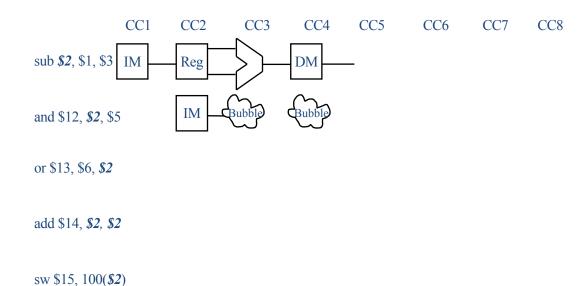

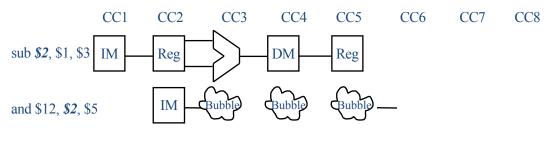

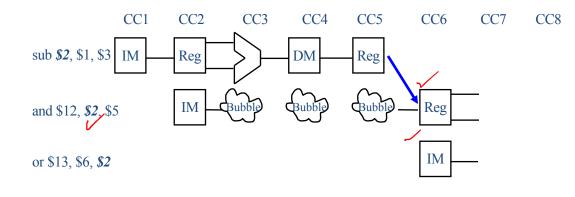

- sub \$2, \$1, \$3

and \$4, \$2, \$5

or \$8, \$2, \$6

add \$9, \$4, \$2

slt \$1, \$6, \$7

- A data hazard results when there is a data dependence between two instructions that appear too close together in the pipeline

- We will define a data hazard as any data dependence that requires either the software or hardware to take special action to get correct

## **Dealing With Data Hazards – What can we do...**

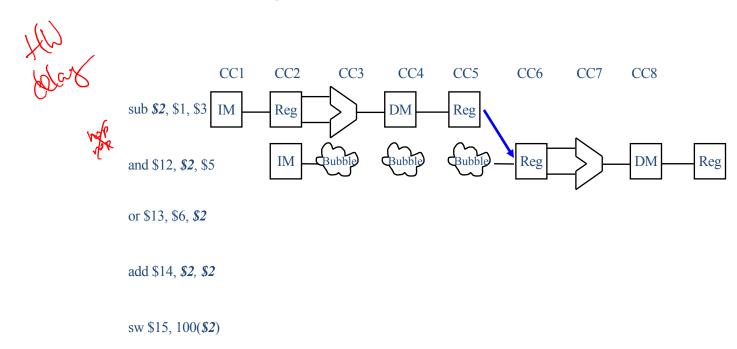

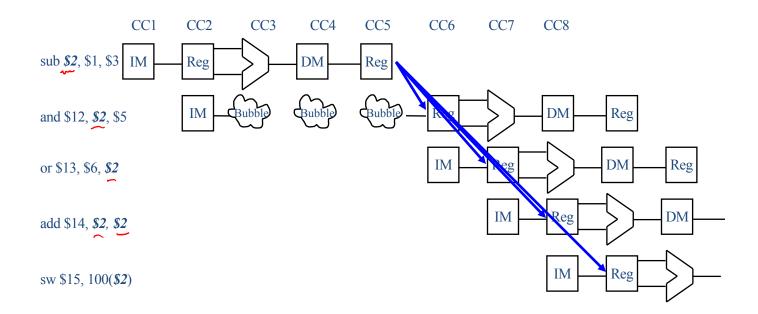

... in Software? • clean n - add no-sp (nop) - use control signals to introduce adelug ...in Hardware? delay n ۲ no delap? : - "forward" Data Hazards are caused by *instruction dependences*. For example, the add is data-dependent on the subtract: subi \$5, \$4, #45 add \$8, \$5, \$2 lm X

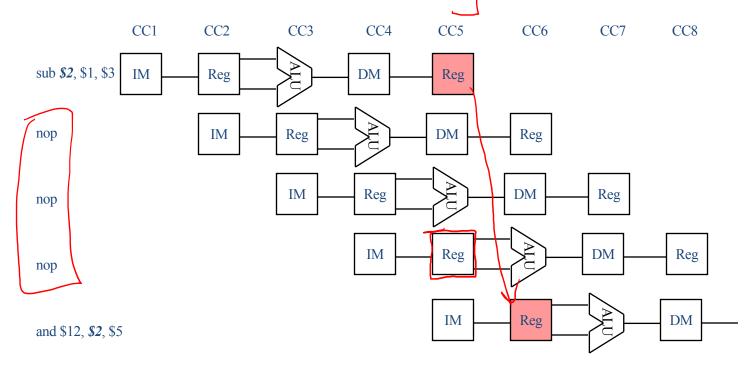

## **Dealing with Data Hazards in Software**

## Dealing with Data Hazards in Software

## How Many No-ops?

sub \$2, \$1,\$3 and \$4, \$2,\$5 or \$8, \$2,\$6 add \$9, \$4,\$2 slt \$1, \$6,\$7

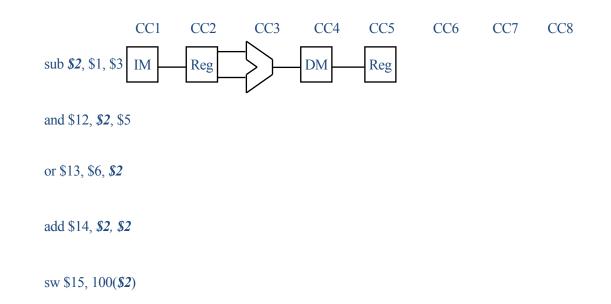

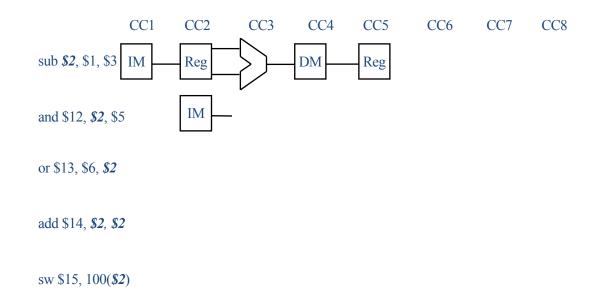

## Are No-ops Really Necessary?

sub \$2, \$1,\$3 and \$4, \$2,\$5 or \$8, \$3,\$6 add \$9, \$2,\$8 slt \$1, \$6,\$7

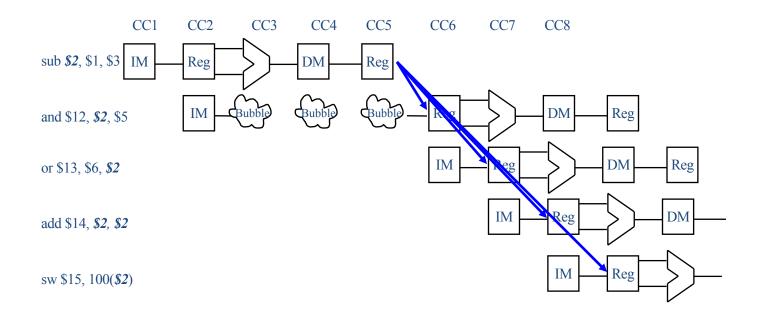

sw \$15, 100(**\$2**)

or \$13, \$6, **\$2**

add \$14, **\$2**, **\$2**

sw \$15, 100(**\$2**)

add \$14, *\$2, \$2*

sw \$15, 100(**\$2**)

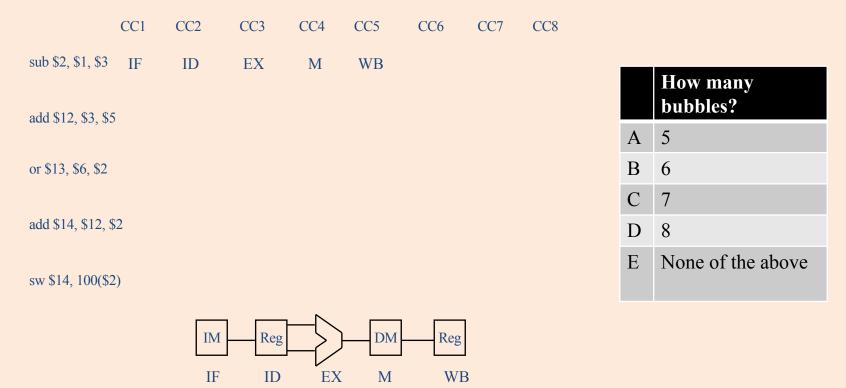

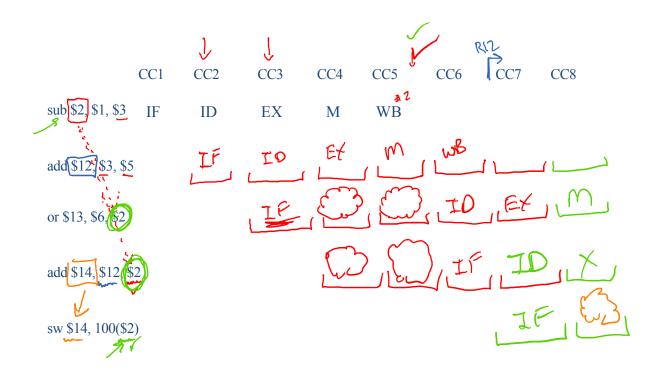

# Poll Q: Try it yourself

# Working this example...

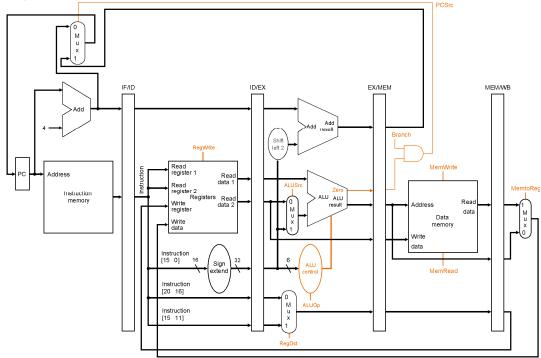

# Poll Q: How to actually implement this in hardware?

Once you detect the hazard in ID - what must you do to insert the nop and "stall"?

Flush <u>all instructions in the pipeline</u> (set control signals to 0).

Set all control signals going to ID/EX register to zero.

Set PCWrite to zero.

Set IF/ID register write to zero.

|           | Selection | Changes           |

|-----------|-----------|-------------------|

|           | А         | 1, 3, 4           |

|           | В         | 1, 2, 3           |

| $\langle$ | C         | 2, 3, 4           |

|           | D         | 1                 |

|           | Е         | None of the above |

# **Pipeline Stalls**

- To ensure proper pipeline execution in light of register dependences, we must:

- detect the hazard

- stall the pipeline

## **Knowing When to Stall**

## **Knowing When to Stall**

# **The Pipeline**

• What comparisons tell us when to stall?