# CSE 141L: Introduction to Computer Architecture Lab **SystemVerilog**

Pat Pannuto, UC San Diego

ppannuto@ucsd.edu

CSE 141L

CC BY-NC-ND Pat Pannuto – Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and other

## **Logistics Updates**

- Lab Hours

- Internal signups for CSE basement labs end today

- Expect to post hours beginning of next week

- Trickling in on Canvas now, but subject to change still...

- Tools

- CloudLabs is live

- ModelSim is dead, long live Questa [but ModelSim is fine too]

- When following tutorials, seems safe to **s/ModelSim/Questa**

- Vocabulary

- Labs -> Milestones + Final Report

#### **Logistics Update: Waitlists**

- 24 people and counting who are in/finished 141 but waitlisted for 141L

- This is too many to just let everyone in

#### If you are considering dropping this course, <u>please</u> do so ASAP

- If you are far back on the waitlist for 141, then please make room in 141L

- 141 <u>will</u> be offered next quarter

- (I'm teaching it)

## SYNTHESIZABLE SYSTEM VERILOG 1 – FUNDAMENTALS

CC BY-NC-ND Pat Pannuto - Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and others

## What is SystemVerilog (SV)?

- In this class and in the real world, SystemVerilog is a specification language, not a programming language.

- Draw your schematic and state machines and then transcribe it into SV.

- When you sit down to write SV you should know exactly what you are implementing.

- We are constraining you to a subset of the language for two reasons

- These are the parts that people use to design real processors

- Steer you clear of problematic constructs that lead to bad design.

## [System]Verilog is a Hardware Description Language (HDL)

- The other popular HDL is VHDL

- An HDL is not a programming language it is an HDL!

- SystemVerilog is a new-ish improvement over Verilog

- Technically, it's a backwards-compatible superset

- This can be troublesome, as Verilog is earlier to make mistakes in :/

## **SV Fundamentals**

- What is System Verilog?

- Data types

- Structural SV

- RTL SV

- Combinational Logic

- Sequential Logic

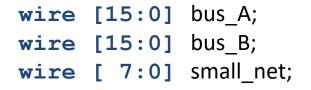

## Bit-vectors are the primary data type in Synthesizable SV

A bit can take on one of four values

| Value | Meaning                  |

|-------|--------------------------|

| 0     | Logic zero               |

| 1     | Logic one                |

| ► X   | Unknown logic value      |

| Z     | High impedance, floating |

In the simulation waveform viewer, Unknown signals are RED. There should be no red after reset.

An X bit might be a 0, 1, Z, or in transition. We can set bits to be X in situations where we don't care what the value is. This can help catch bugs and improve synthesis quality.

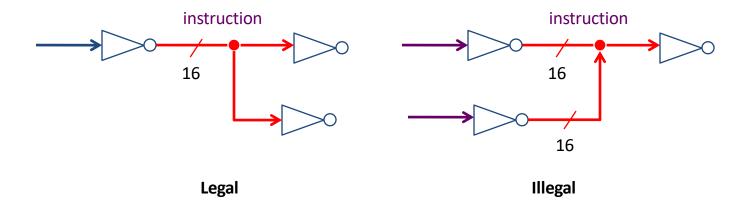

# logic keyword denotes a hardware net that has a single driver but possibly multiple outputs

• It can be combinational or sequential – other syntax will tell which

```

logic [15:0] instruction;

```

## wire keyword denotes a hardware net that has >=1 drivers, or that has unknown (or bi-) directionality

Absolutely no type safety when connecting nets!

CC BY-NC-ND Pat Pannuto – Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and other

## **Bit literals**

## 4'b10 11 Underscores are ignored Base format (d,b,o,h) Decimal number

representing size in bits

We'll learn how to actually assign literals to nets a little later

- Binary literals

- 8'b0000\_0000

- $-8'b0xx0_1xx1$

- Hexadecimal literals

- $-32'h0a34_def1$

- -16' haxxx

- Decimal literals

– 32′ d42

## **SV Fundamentals**

- What is System Verilog?

- Data types

- Structural SV

- RTL SV

- Combinational Logic

- Sequential Logic

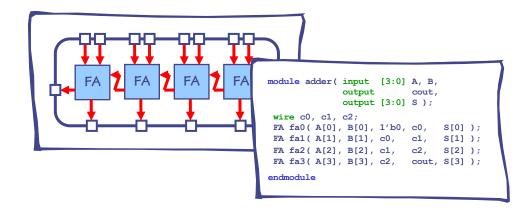

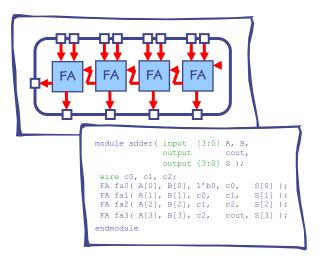

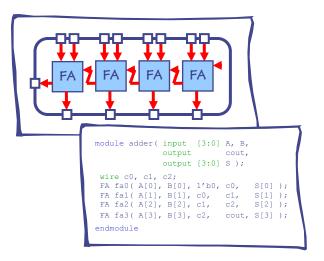

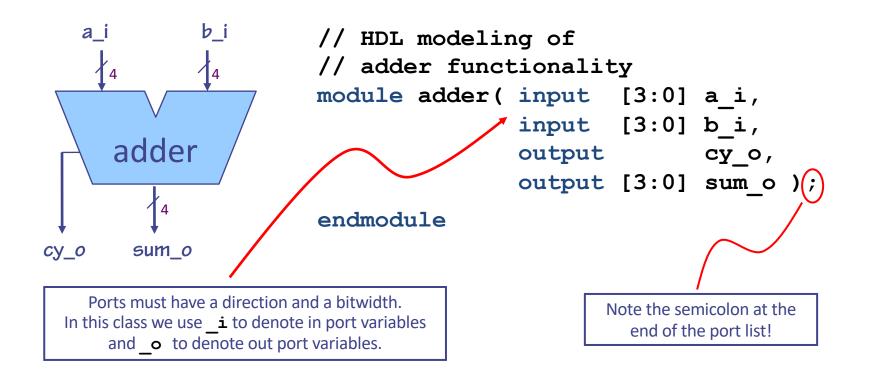

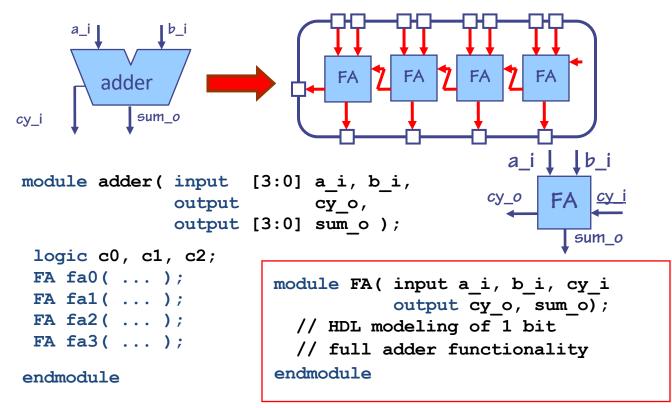

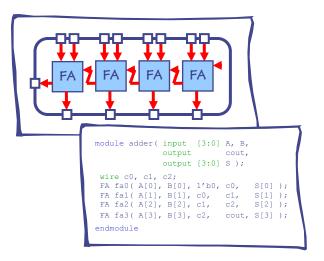

#### A SV module has a name and a port list

#### A module can instantiate other modules

#### **Connecting modules**

#### Only connect ports by name and not by position.

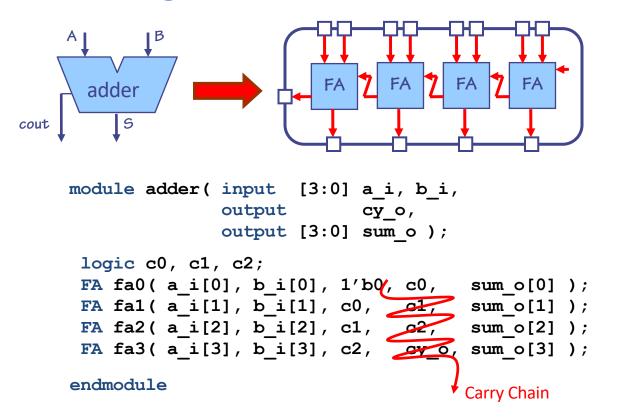

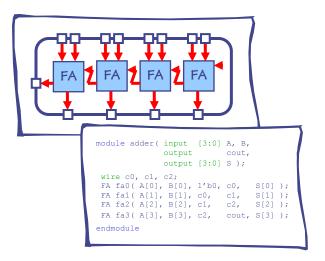

**Connecting ports by ordered list** is compact but bug prone:

```

FA fa0( a_i[0], b_i[0], 1'b0, c0, sum_o[0] );

```

**Connecting by name** is less compact but leads to fewer bugs. This is how you should do it in this class. You should also line up like parameters so it is easy to check correctness.

```

FA fa0( .a_i(a_i[0])

,.b_i(b_i[0])

,.cy_i(1'b0)

,.cy_o(c0)

,.sum_o(sum_o[0])

);

```

Connecting ports by name yields clearer and less buggy code. In the slides, we may do it by position for space. But you should do it by name and not position.

## **SV Fundamentals**

- What is System Verilog?

- Data types

- Structural SV

- RTL SV

- Combinational Logic

- Sequential Logic

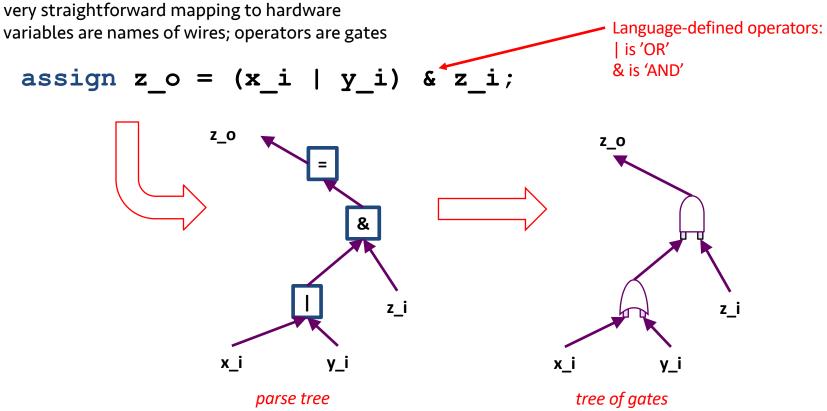

## Combinational Verilog: assign

CC BY-NC-ND Pat Pannuto – Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and other

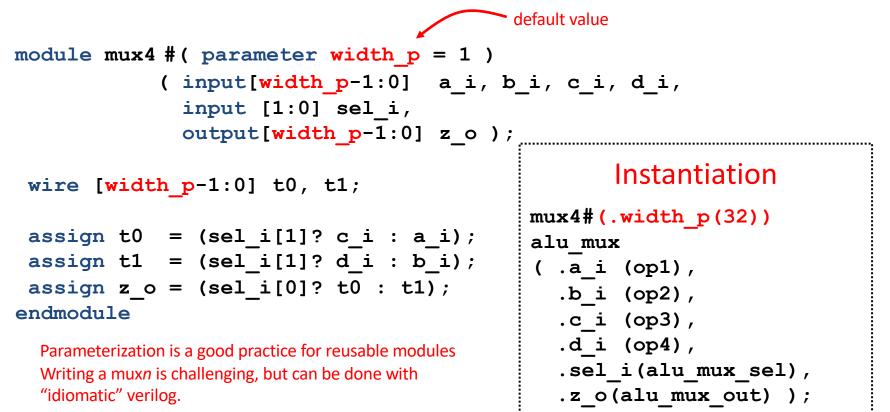

#### A module's behaviour can be described in many different ways but it should not matter from outside

Example: mux4

CC BY-NC-ND Pat Pannuto - Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and others

mux4:

#### Using continuous assignments to generate combinational logic

| <pre>module mux4( input a_i, b_i, c_i, d_i,</pre>                                                                                                          | A couple of combinational<br>trees that<br>connect to each<br>other |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| <pre>logic t0, t1;</pre>                                                                                                                                   |                                                                     |

| <pre>assign z_o = ~((t0   sel_i[0]) &amp; (t1   ~s<br/>assign t1 = ~((sel_i[1] &amp; d_i)   (~sel_i<br/>assign t0 = ~((sel_i[1] &amp; c_i)   (~sel_i</pre> | .[1] & b_i));                                                       |

| The order of these continuous <b>assign</b> statements functionality – they are just specifying a bunch of gate                                            |                                                                     |

endmodule

Any time an input to the combinational cloud changes, it propagates through the cloud of gates and the outputs are updated. (Be careful not to create combinational cycles!)

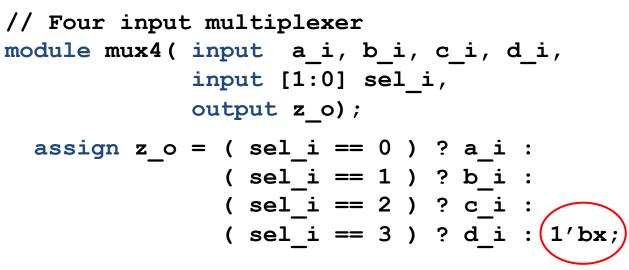

mux4: Using ? :

#### endmodule

If **sel\_i** is X or Z, without the 1'bX condition, it would get d\_i in behavioural simulation but maybe not in timing. Bad!

Having the 1'bx will help make sure your timing simulation looks the same as your behavioural.

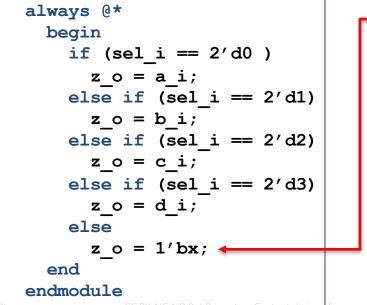

#### mux4:

## Using combinational always\_comb or always @(\*) block

always\_comb // system verilog; replaces always @(\*)

begin

```

t0 = (sel_i[1] & c_i) | (~sel_i[1] & a_i);

t1 = ~((sel_i[1] & d_i) | (~sel_i[1] & b_i));

t0 = ~t0;

z_o = ~( (t0 | sel_i[0]) & (t1 | ~sel_i[0]) );

```

end

endmodule

<u>Within</u> the always\_comb block, the synthesis tool synthesizes the lines in order. Each L-value (variable to the left of =) creates a name for the wire that is at the top of a logic tree. If a variable is assigned again (like t0), then the mapping is updated – no cycles are created.

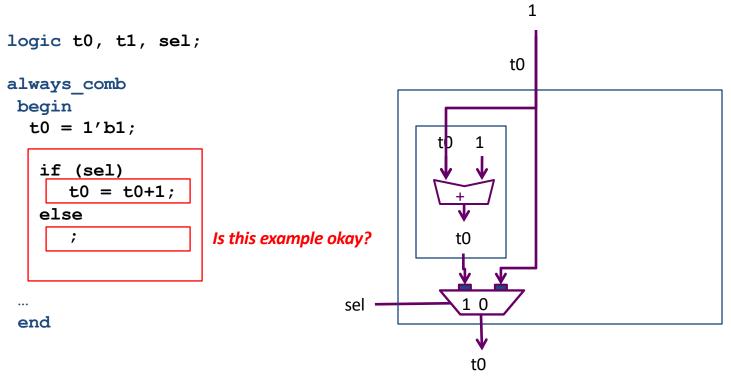

#### always\_comb permits more advanced combinational idioms

Good idea for avoiding behavioral versus timing mismatches.

If none of these match, behavioral will just use last value. Timing will give you an X probably.

CC BY-NC-ND Pat Pannuto – Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and others

#### end

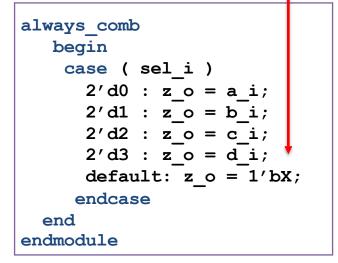

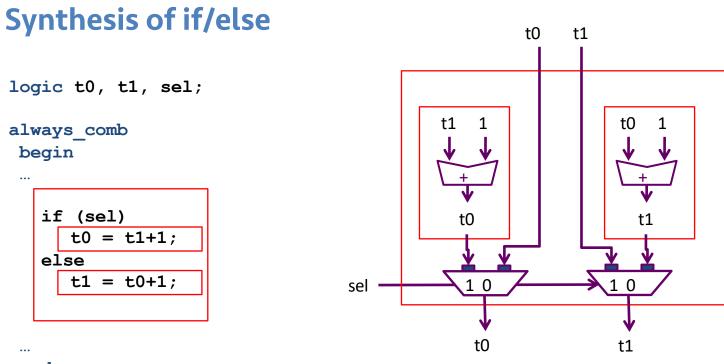

#### Note: a mux is created for every L-value written by all branches of the if/else or case statement.

#### Note: no L-value should be undefined on any path; behavior is undefined; Verilog will create a latch (ugh)!

#### Synthesis of if/else

#### What happens if the case statement is not complete?

```

module mux3( input a i, b i, c i,

input [1:0] sel i,

output logic z o );

always @( * )

begin

case ( sel i )

2'd0 : z o = a i;

If sel = 3, mux will output

2'd1 : z o = b i;

the previous value!

2'd2 : z o = c i;

endcase

What have we created?

end

endmodule

```

#### What happens if the case statement is not complete?

```

module mux3( input a i, b i, c i

input [1:0] sel i,

output logic z o );

always @( * )

begin

We CAN prevent creating a latch

case ( sel i )

2'd0 : z \circ = a i; with a default statement

2'd1 : z o = b i;

2'd2 : z o = c i;

default : z \circ = 1'bx;

endcase

end

endmodule

```

#### What happens if the case statement is not complete?

always @( \* )

```

SystemVerilog will protect you!

```

```

always_comb

```

```

begin

case ( sel_i )

2'd0 : z_o = a_i;

2'd1 : z_o = b_i;

2'd2 : z_o = c_i;

default : z_o = 1'bx;

endcase

end

```

Be wary, many examples online are still plain ol' Verilog, and will work fine ... until they don't ☺

#### endmodule

#### **Parameterized mux4**

## **SV Fundamentals**

- What is System Verilog?

- Data types

- Structural SV

- RTL SV

- Combinational Logic

- Sequential Logic

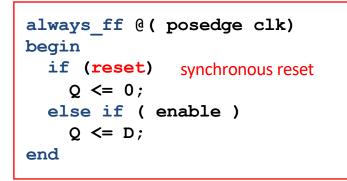

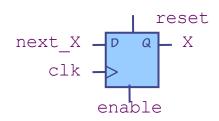

## Sequential Logic: Creating a flip flop

```

note: always use <= with always_ff and = with always_comb

logic q_r, q_n;

logic q_r, q_n;

always_ff <sup>3</sup>@( posedge clk )

q_r <= q_n;</pre>

```

1) This line simply creates two signals, one called  $\mathbf{q}_{\mathbf{r}}$  and the other called  $\mathbf{q}_{\mathbf{n}}$ .

2) **always\_ff** keyword indicates our intent to create registers; you could use the **always** keyword instead, but this makes it clear what you want!

3) @ ( **posedge clk** ) indicates that we want these registers to be triggered on the positive edge of the **clk** clock signal.

4) Combined with 2) and 3), the <= creates a register whose input is wired to **q\_n** and whose output is wired to **q\_r**. Use **r** to indicate a wire that comes directly out of a register, and **n** (i.e., next) to indicate a wire that goes directly into one, and becomes the new output on the next cycle.

#### Sequential Logic: flip-flop idioms

#### idiom: flip-flops with reset

#### Register (i.e. a vector of parallel flip-flops)

```

module register#(parameter width p = 1)

input clk,

input [width p-1:0] d i,

input en i,

output logic [width p-1:0] q r o

);

always ff @( posedge clk )

begin

if (en i)

q r o <= d i;

end

```

endmodule

#### **Implementing Wider Registers**

```

module register2

(input clk,

input [1:0] d i,

input en i,

output logic [1:0] q r o

);

always ff @ (posedge clk)

begin

if (en i)

q r o <= d i;

end

endmodule

Do they behave the same?

```

```

module register2

(input clk,

input [1:0] d i,

input en i,

output logic [1:0] q r o

);

FF ff0 (.clk(clk),

.d i(d i[0]),

.en i(en i),

.qro(qro[0]));

FF ff1 (.clk(clk),

.d i(d i[1]),

.en i(en i),

.qro(qro[1]));

endmodule

```

ves

## Syntactic Sugar: always\_ff allows you to combine combinational and sequential logic; but this can be confusing.

#### more clear

```

module accum #(parameter width_p=1)

( input clk,

input data_i,

input en_i,

output logic [width_p-1:0] sum_o;

);

```

```

logic [width_p-1:0] sum_r, sum_next;

assign sum_o = sum_r;

```

```

always_comb

begin

sum_next = sum_r;

```

```

if (en_i)

sum_next = sum_r + data_i;

end

```

```

always_ff @(posedge clk)

sum r <= sum next;</pre>

```

#### shorter

```

module accum #(parameter width_p=1)

( input clk,

input data_i,

input en_i,

output logic [width_p-1:0] sum_o;

);

```

```

logic [width_p-1:0] sum_r;

assign sum_o = sum_r;

```

```

always_ff @(posedge clk)

begin

if (en_i)

sum_r <= sum_r + data_i;

end</pre>

```

Syntactic Sugar: You can always convert an always\_ff that combines combinational and sequential logic into two separate always\_ff and always\_comb blocks.

#### shorter

```

module accum #(parameter width_p=1)

( input clk,

input data_i,

input en_i,

output logic [width_p-1:0] sum_o;

);

```

```

logic [width_p-1:0] sum_r;

assign sum o = sum r;

```

```

always_ff @(posedge clk)

begin

if (en_i)

sum_r <= sum_r + data_i;

end</pre>

```

#### more clear

```

module accum #(parameter width_p=1)

( input clk,

input data_i,

input en_i,

output logic [width_p-1:0] sum_o;

);

reg [width_p-1:0] sum_r, sum_next;

assign sum_o = sum_r;

always_comb

begin

sum_next = sum_r;

```

```

if (en_i) 2a

sum_next = sum_r + data_i;

end

```

```

always_ff @(posedge clk)

sum_r <= sum_next;</pre>

```

#### When in doubt, use the version on the right.

To go from the left-hand version to the right one: 1. For each register **xxx\_r**, introduce a temporary variable that holds the input to each register (e.g.

#### xxx\_next)

2. Extract the combinational part of the

always\_ff block into an always\_comb

block:

```

a. change xxx_r <= to xxx_next =

b. add xxx_next = xxx_r; to

beginning of block for default case

3. Extract the sequential part of the

always_ff by creating a separate

always_ff that does xxx_r <=

xxx next;</pre>

```

## **Register array: we recommend you retain the** en\_i **idiom in the** always\_ff **block - could reduce # of ports.**

shorter

more clear

always\_ff @(posedge clk)

if (en\_i)

sum\_r[wr\_i] <= foo + far;

end</pre>

always\_comb

begin

sum\_cond\_next = foo + far;

```

always_ff @(posedge clk)

if (en_i)

sum_r[wr_i] <= sum_cond_next;</pre>

```

shorter

extra ports? not so good.

```

always_ff @(posedge clk)

if (en_i)

sum_r[wr_i] <= foo + far;

en_i ? (foo + far) : sum_r[wr_i];

end

always ff @(posedge clk)</pre>

```

```

sum_r[wr_i] <= sum_cond_next;</pre>

```

#### **Bit Manipulations**

```

logic [15:0] x;

logic [31:0] x_sext;

logic [31:0] hi, lo;

logic [63:0] hilo;

```

```

// concatenation

assign hilo = { hi, lo};

assign { hi, lo } = { 32'b0, 32'b1 };

// duplicate bits (16 copies of x[15] + bits 15..0 of x)

assign x_sext = {{16 { x[15] }}, x[15:0]};

// select top_p bits starting at 0 (same as [top_p-1:0])

assign foo = x[0+:top p];

```

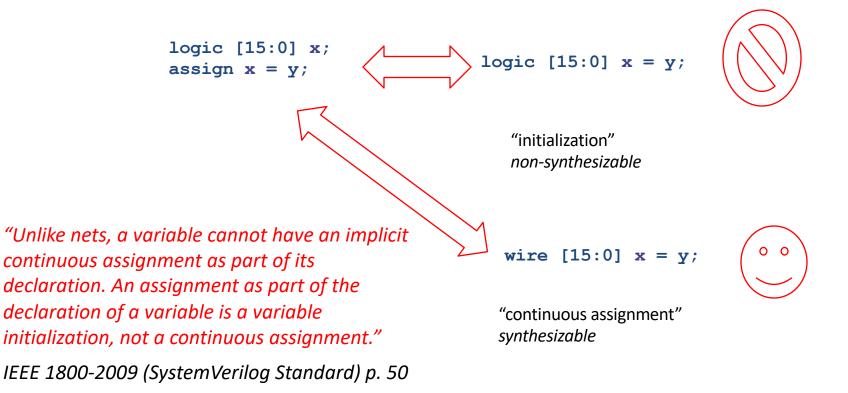

#### **Beware of assignment shortcuts**

CSE 141L

## unique and priority for case and if

unique exactly one branch or case item must execute; otherwise it is an error.

#### priority choices **must** be **evaluated in orde**r, and that **one branch must execute**.

Synopsys VCS: Does not generate X output, just says:

RT Warning: No condition matches in 'unique case' statement. "system.v", line 20, for testbench.dut.cu, at time 100.

So, using 1'bX as the default condition still has some purpose, since it shows up in the waveform viewer. On the other hand, this tells you when the issue happens.

#### **Note: Our SV Subset**

- SV is a big language with many features not concerned with synthesizing hardware.

- The code you write for your processor should contain only the language structures discussed in these slides.

- Anything else is not synthesizable, although it will simulate fine.

- We will be mixing in some more synthesizable SystemVerilog later in the course to improve maintainability of your code.