## CSE 141L: Introduction to Computer Architecture Lab SystemVerilog II

Pat Pannuto, UC San Diego

ppannuto@ucsd.edu

CSE 141L

CC BY-NC-ND Pat Pannuto – Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and other

### Milestone 1 is due in 48 hours [before class Wed]

- What to submit?

- <u>SOMETHING</u>

- M1 is graded for completion, not accuracy

- The purpose of milestones is to *help you* manage large, long-term project

- TAs will use gradescope "grades" to help give feedback

- Recall: Only Milestone 4 (final submission) is actual grade\*

- \*With exceptions for things such as skipping milestones altogether

### Today's Objectives: Learning more about SystemVerilog

- We'll get through ~half+ these slides today, and the rest on Wednesday

- Treat these slides as a reference

- It'll go kind of fast, goal is to expose to you things you can learn more about on your own

### Logistics Updates — Course Modality Poll

- Not matter what, remote attendance will be an option all quarter

- Will always stream via Zoom and recordings in Canvas

- Current guidance is that we *can* resume in-person instruction next week

- We are also permitted up to 5 weeks to shift modality

- And this class does not meet during week 10 [all project hours]

- **POLL**: Would you come to CENTR 115 M/W from 12-1 every day?

- A: Definitely Yes

- B: Maybe leaning Yes

- C: Maybe leaning No

- D: Definitely No

[Picking this back up from week 1]

# SYNTHESIZABLE SYSTEM VERILOG I – FUNDAMENTALS

### A module's behaviour can be described in many different ways but it should not matter from outside

Example: mux4

CC BY-NC-ND Pat Pannuto - Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and others

mux4:

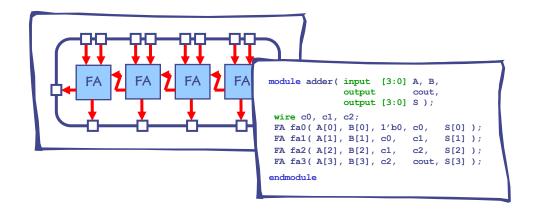

#### Using continuous assignments to generate combinational logic

| <pre>module mux4( input a_i, b_i, c_i, d_i,</pre>                                                                                                                                    | A couple of combinational<br>trees that<br>connect to each<br>other |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| <pre>logic t0, t1;</pre>                                                                                                                                                             |                                                                     |

| <pre>assign z_o = ~((t0   sel_i[0]) &amp; (t1   ~s<br/>assign t1 = ~((sel_i[1] &amp; d_i)   (~sel_i<br/>assign t0 = ~((sel_i[1] &amp; c_i)   (~sel_i</pre>                           | .[1] & b_i));                                                       |

| The order of these continuous <b>assign</b> statements in the source code does not affect functionality – they are just specifying a bunch of gates – <i>a combinational cloud</i> . |                                                                     |

endmodule

Any time an input to the combinational cloud changes, it propagates through the cloud of gates and the outputs are updated. (Be careful not to create combinational cycles!)

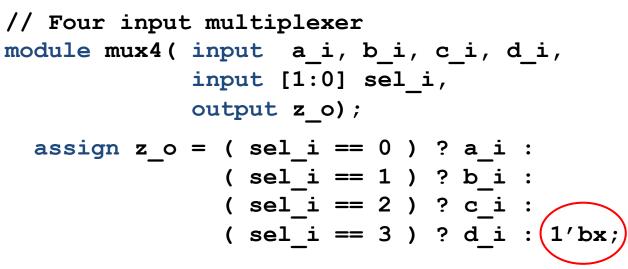

mux4: Using ? :

endmodule

If **sel\_i** is X or Z, without the 1'bX condition, it would get d\_i in behavioural simulation but maybe not in timing. Bad!

Having the 1'bx will help make sure your timing simulation looks the same as your behavioural.

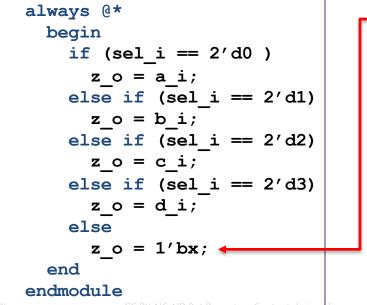

#### mux4:

### Using combinational always\_comb or always @(\*) block

always\_comb // system verilog; replaces always @(\*)

begin

```

t0 = (sel_i[1] & c_i) | (~sel_i[1] & a_i);

t1 = ~((sel_i[1] & d_i) | (~sel_i[1] & b_i));

t0 = ~t0;

z_o = ~( (t0 | sel_i[0]) & (t1 | ~sel_i[0]) );

```

end

endmodule

<u>Within</u> the always\_comb block, the synthesis tool synthesizes the lines in order. Each L-value (variable to the left of =) creates a name for the wire that is at the top of a logic tree. If a variable is assigned again (like t0), then the mapping is updated – no cycles are created.

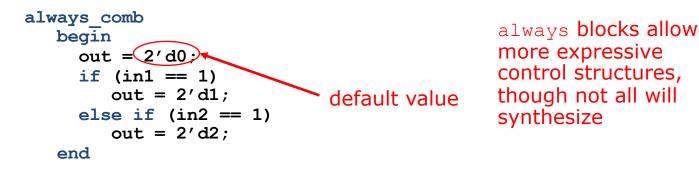

#### always\_comb permits more advanced combinational idioms

Good idea for avoiding behavioral versus timing mismatches.

If none of these match, behavioral will just use last value. Timing will give you an X probably.

CC BY-NC-ND Pat Pannuto – Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and others

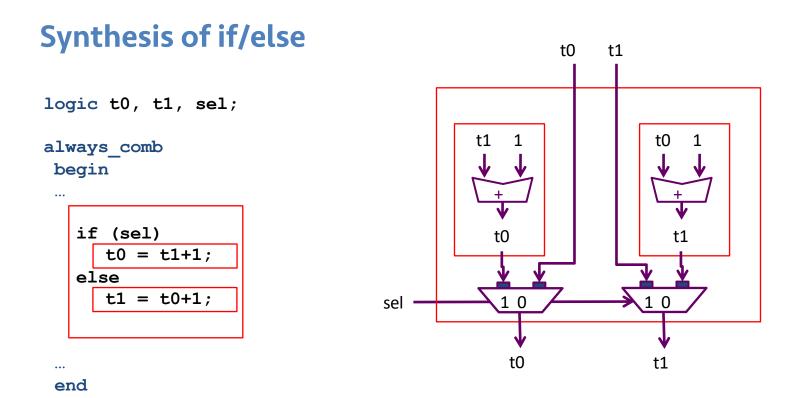

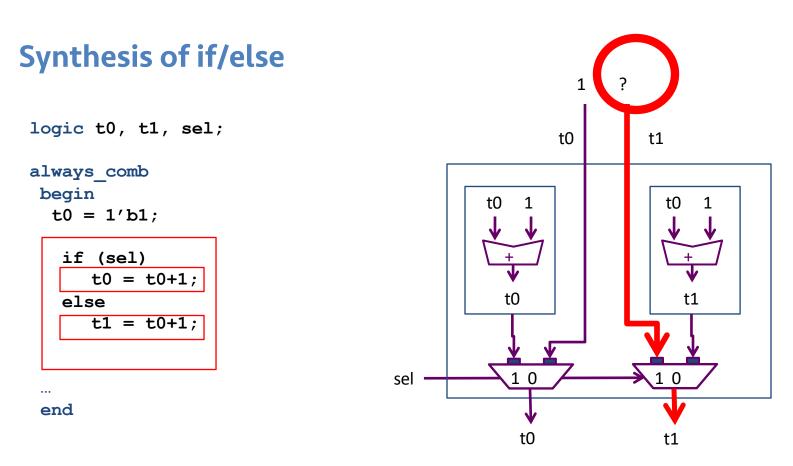

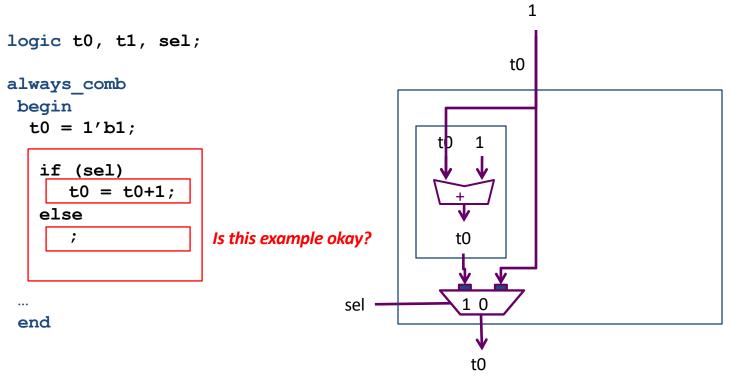

#### Note: a mux is created for every L-value written by all branches of the if/else or case statement.

#### Note: no L-value should be undefined on any path; behavior is undefined; Verilog will create a latch (ugh)!

#### Synthesis of if/else

#### What happens if the case statement is not complete?

```

module mux3( input a i, b i, c i,

input [1:0] sel i,

output logic z o );

always @( * )

begin

case ( sel i )

2'd0 : z o = a i;

If sel = 3, mux will output

2'd1 : z o = b i;

the previous value!

2'd2 : z o = c i;

endcase

What have we created?

end

endmodule

```

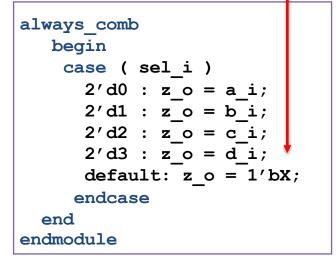

#### What happens if the case statement is not complete?

```

module mux3( input a i, b i, c i

input [1:0] sel i,

output logic z o );

always @( * )

begin

We CAN prevent creating a latch

case ( sel i )

2'd0 : z \circ = a i; with a default statement

2'd1 : z o = b i;

2'd2 : z o = c i;

default : z \circ = 1'bx;

endcase

end

endmodule

```

#### What happens if the case statement is not complete?

default :  $z \circ = 1'bx;$

always @( \* )

```

SystemVerilog will protect you!

```

```

always_comb

```

```

begin

case ( sel_i )

2'd0 : z_o = a_i;

2'd1 : z_o = b_i;

2'd2 : z o = c i;

```

endcase

Be wary, many examples online are still plain ol' Verilog, and will work fine ... until they don't ☺

#### end

#### endmodule

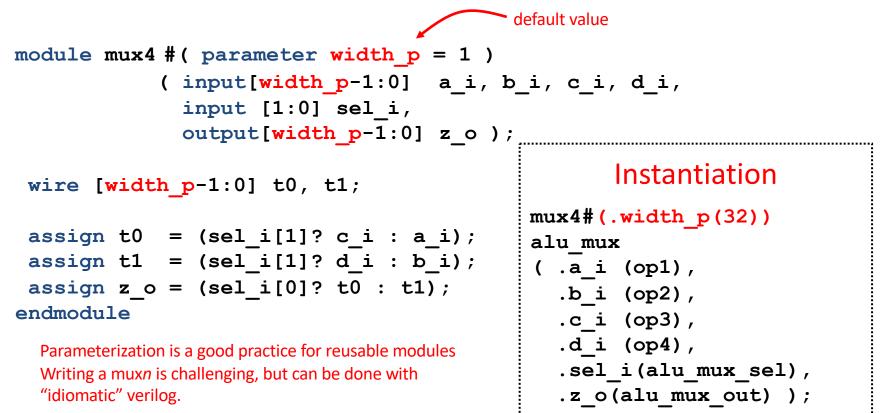

#### **Parameterized mux4**

### **SV Fundamentals**

- What is System Verilog?

- Data types

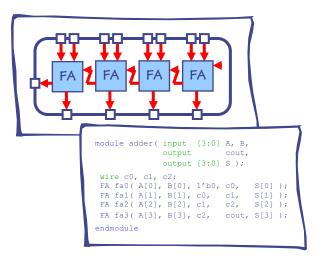

- Structural SV

- RTL SV

- Combinational Logic

- Sequential Logic

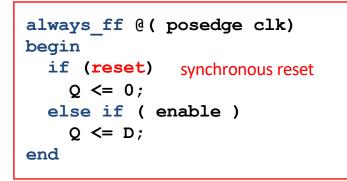

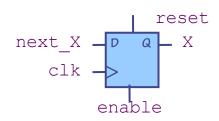

### Sequential Logic: Creating a flip flop

```

note: always use <= with always_ff and = with always_comb

logic q_r, q_n;

logic q_r, q_n;

always_ff <sup>3</sup>@( posedge clk )

q_r <= q_n;</pre>

```

1) This line simply creates two signals, one called  $\mathbf{q}_{\mathbf{r}}$  and the other called  $\mathbf{q}_{\mathbf{n}}$ .

2) **always\_ff** keyword indicates our intent to create registers; you could use the **always** keyword instead, but this makes it clear what you want!

3) @ ( **posedge clk** ) indicates that we want these registers to be triggered on the positive edge of the **clk** clock signal.

4) Combined with 2) and 3), the <= creates a register whose input is wired to **q\_n** and whose output is wired to **q\_r**. Use **r** to indicate a wire that comes directly out of a register, and **n** (i.e., next) to indicate a wire that goes directly into one, and becomes the new output on the next cycle.

#### Sequential Logic: flip-flop idioms

### idiom: flip-flops with reset

#### Register (i.e. a vector of parallel flip-flops)

```

module register#(parameter width p = 1)

input clk,

input [width p-1:0] d i,

input en i,

output logic [width p-1:0] q r o

);

always ff @( posedge clk )

begin

if (en i)

q r o <= d i;

end

```

endmodule

#### **Implementing Wider Registers**

```

module register2

(input clk,

input [1:0] d i,

input en i,

output logic [1:0] q r o

);

always ff @(posedge clk)

begin

if (en i)

q r o <= d i;

end

endmodule

Do they behave the same?

```

```

module register2

(input clk,

input [1:0] d i,

input en i,

output logic [1:0] q r o

);

FF ff0 (.clk(clk),

.d i(d i[0]),

.en i(en i),

.qro(qro[0]));

FF ff1 (.clk(clk),

.d i(d i[1]),

.en i(en i),

.qro(qro[1]));

endmodule

```

ves

# Syntactic Sugar: always\_ff allows you to combine combinational and sequential logic; but this can be confusing.

#### more clear

```

module accum #(parameter width_p=1)

( input clk,

input data_i,

input en_i,

output logic [width_p-1:0] sum_o;

);

```

```

logic [width_p-1:0] sum_r, sum_next;

assign sum_o = sum_r;

```

```

always_comb

begin

sum_next = sum_r;

```

```

if (en_i)

sum_next = sum_r + data_i;

end

```

```

always_ff @(posedge clk)

sum r <= sum next;</pre>

```

#### shorter

```

module accum #(parameter width_p=1)

( input clk,

input data_i,

input en_i,

output logic [width_p-1:0] sum_o;

);

```

```

logic [width_p-1:0] sum_r;

assign sum_o = sum_r;

```

```

always_ff @(posedge clk)

begin

if (en_i)

sum_r <= sum_r + data_i;

end</pre>

```

Syntactic Sugar: You can always convert an always\_ff that combines combinational and sequential logic into two separate always\_ff and always\_comb blocks.

#### shorter

```

module accum #(parameter width_p=1)

( input clk,

input data_i,

input en_i,

output logic [width_p-1:0] sum_o;

);

```

```

logic [width_p-1:0] sum_r;

assign sum o = sum r;

```

```

always_ff @(posedge clk)

begin

if (en_i)

sum_r <= sum_r + data_i;

end</pre>

```

#### more clear

```

module accum #(parameter width_p=1)

( input clk,

input data_i,

input en_i,

output logic [width_p-1:0] sum_o;

);

reg [width_p-1:0] sum_r, sum_next;

assign sum_o = sum_r;

always_comb

begin

sum_next = sum_r;

```

```

if (en_i) 2a

sum_next = sum_r + data_i;

end

```

```

always_ff @(posedge clk)

sum_r <= sum_next;</pre>

```

#### When in doubt, use the version on the right.

To go from the left-hand version to the right one: 1. For each register xxx\_r, introduce a temporary variable that holds the input to each register (e.g. xxx next)

2. Extract the combinational part of the always\_ff block into an always\_comb block:

```

a. change xxx_r <= to xxx_next =

b. add xxx_next = xxx_r; to

beginning of block for default case

3. Extract the sequential part of the

always_ff by creating a separate

always_ff that does xxx_r <=

xxx next;</pre>

```

# **Register array: we recommend you retain the** en\_i **idiom in the** always\_ff **block - could reduce # of ports.**

shorter

more clear

always\_ff @(posedge clk)

if (en\_i)

sum\_r[wr\_i] <= foo + far;

end</pre>

always\_comb

begin

sum\_cond\_next = foo + far;

```

always_ff @(posedge clk)

if (en_i)

sum_r[wr_i] <= sum_cond_next;</pre>

```

shorter

extra ports? not so good.

```

always_ff @(posedge clk)

if (en_i)

sum_r[wr_i] <= foo + far;

en_i ? (foo + far) : sum_r[wr_i];

end

always ff @(posedge clk)</pre>

```

```

sum_r[wr_i] <= sum_cond_next;</pre>

```

#### **Bit Manipulations**

```

logic [15:0] x;

logic [31:0] x_sext;

logic [31:0] hi, lo;

logic [63:0] hilo;

```

```

// concatenation

assign hilo = { hi, lo};

assign { hi, lo } = { 32'b0, 32'b1 };

// duplicate bits (16 copies of x[15] + bits 15..0 of x)

assign x_sext = {{16 { x[15] }}, x[15:0]};

// select top_p bits starting at 0 (same as [top_p-1:0])

assign foo = x[0+:top p];

```

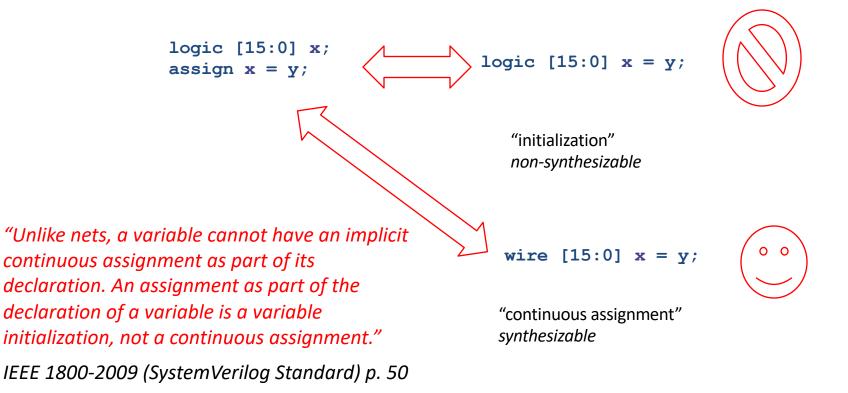

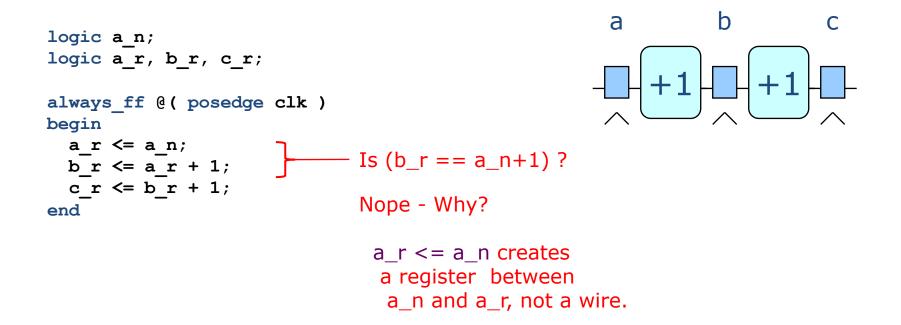

#### **Beware of assignment shortcuts**

CSE 141L

### unique and priority for case and if

unique exactly one branch or case item must execute; otherwise it is an error.

#### priority choices **must** be **evaluated in orde**r, and that **one branch must execute**.

Synopsys VCS: Does not generate X output, just says:

RT Warning: No condition matches in 'unique case' statement. "system.v", line 20, for testbench.dut.cu, at time 100.

So, using 1'bX as the default condition still has some purpose, since it shows up in the waveform viewer. On the other hand, this tells you when the issue happens.

#### **Note: Our SV Subset**

- SV is a big language with many features not concerned with synthesizing hardware.

- The code you write for your processor should contain only the language structures discussed in these slides.

- Anything else is not synthesizable, although it will simulate fine.

# SYSTEM VERILOG II – DESIGN EXAMPLES

CC BY-NC-ND Pat Pannuto - Content derived from materials from John Eldon, Dean Tullsen, Steven Swanson, and others

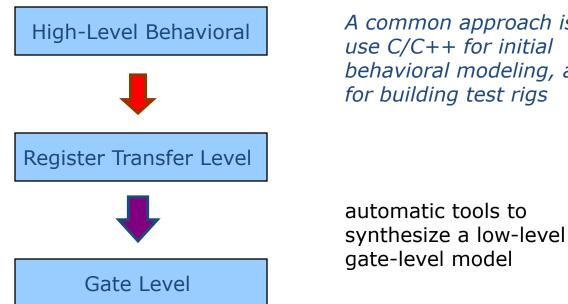

#### Verilog can be used at several levels

A common approach is to use C/C++ for initial behavioral modeling, and for building test rigs

### **Recap: Combinational logic**

- Use continuous assignments (assign) assign c i = b o + 1;

- Use **always\_comb** blocks with blocking assignments (=)

- Every variable should have a *default value* to avoid inadvertent introduction of latches

- Don't assign to same variable from more than one **always** block. Race conditions in behavioral sim, synthesizes incorrectly.

### **Recap: Sequential Logic**

- Use always\_ff @ (posedge clk) only with non-blocking assignment operator (<=)</li>

always\_ff @ ( posedge clk )

c\_o <= c\_i;</li>

- Careful when mixing pos-edge & neg-edge triggered flip-flops

- Do not assign the same variable from more than one always block. Race condition in behavioral simulation; synthesizes incorrectly.

- Do not mix blocking and non-blocking assignments

- only use non-blocking assignments (<=) for sequential logic.

- only use block assignments (=) for combinational logic.

- Like in software engineering, express your design as a module hierarchy that corresponds to logical boundaries in the design. Also, separate datapath and control (more later).

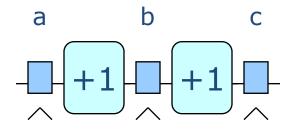

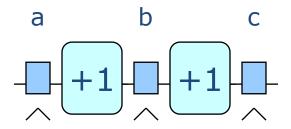

#### An Example: Good Style

```

logic a_n, b_n, c_n;

logic a_r, b_r, c_r;

always_ff @( posedge clk )

begin

```

```

a_r <= a_n;

b_r <= b_n;

c_r <= c_n;

end

```

assign b\_n = a\_r + 1; assign c\_n = b\_r + 1;

Readable, combinational and sequential logic are separated.

Consistent naming: A\_r is the output of the register and A\_n (or A\_n) is the input.

#### **An Example: Good Style**

```

logic a n;

logic b n, c n;

logic ar, br, cr;

always ff @( posedge clk )

begin

ar <= an; // list in any order

b r <= b n;

c r \leq c n;

end

always comb

begin

b n = a r + 1; // triggers when a r or b r changes

c n = b r + 1;

end

```

Readable, combinational and sequential logic are separated.

## Alternate implementation?

```

logic a_n, b_n, c_n;

logic a_r, b_r, c_r;

always_ff @( posedge clk )

begin

a_r <= a_n;

b_r <= b_n;

c_r <= c_n;

assign b_n = a_r + 1;

assign c_n = b_r + 1;

end

```

Syntactically Incorrect.

### An Example: Okay, but less readable?

## Another style – multiple always blocks

```

logic a n, b n, c n;

logic a r, b r, c r;

always ff @( posedge clk )

a r \leq a n;

assign b n = a r + 1;

always ff @( posedge clk )

b r <= b n;

assign c n = b r + 1;

always ff @( posedge clk )

c r \leq c n;

```

Does it have the same functionality?

Yes. But why?

It generates the same underlying circuit.

### How about this one?

Will this synthesize?

→ Maybe

Is it correct?

→ No; Don't use "blocking assignments" in

@posedge clk blocks. It creates race conditions. Also,

use always\_ff instead.

# What does this do? (This is correct but bad code.)

```

logic b_i, c_i;

logic a_r;

logic sel;

always @( posedge clk )

begin

a_r <= 1'b0;

a_r <= b_i;

if (sel)

a_r <= c_i;

ord

```

## Desugar into separate comb. and seq. logic.

logic b\_i, c\_i; logic a\_r; logic sel;

always @( posedge clk )

begin

a\_r <= 1'b0; // redundant!

a\_r <= b\_i;

if (sel)

a\_r <= c\_i;

end</pre>

```

logic a_n, b_i, c_i;

logic a_r;

logic sel;

```

```

always_comb

begin

a_n = a_r; // default;

// rdt. but safe

a_n = b_i;

if (sel)

a_n = c_i;

end

always ff @( posedge clk )

```

```

a_r <= a_n;

```

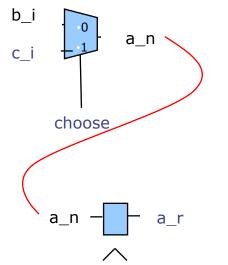

### What does this do?

For each always comb, assign, always ff statement, draw the gates and wires.

```

logic a n, b i, c i;

logic a r;

logic choose;

always comb

begin

a n = a r; // default

a n = b i;

if (choose)

a_n = c i;

end

always ff @( posedge clk )

```

a r <= a n;

# **Verilog execution semantics**

- Confusing

- Best solution is to write synthesizable Verilog that corresponds exactly to logic you have *already* designed on paper. <u>Separate combinational from sequential logic.</u>

- Debugging is difficult for Verilog. Don't write code and "see if it works." Test each "unknown" thing individually until you know what it does; then combine into larger entities.

- Before you try to simulate, manually check every wire to make sure that it is correctly (1) defined, connected to (2) source and (3) destination, and that (4) the logic driving it appears to be correct.

- This is *faster* than finding the same bugs in the waveform viewer!

### **Useful operators: reduction**

(| c) // all of the bits of C or'd together ("or reduce")

(& c) // all of the bits of C and'd together ("and reduce")

(^ c) // all of the bits of C xor'd together ("xor reduce")

## SystemVerilog struct example

```

typedef struct packed {

logic [17-1:0] instr;

logic [10-1:0] addr;

} instr packet s;

instr packet s ip n, ip A r, ip B r, ip C r;

assign ip n = `{addr: addr i

, instr: instr i};

assign { addr o, instr o }

= { ip C r.addr, ip C r.instr };

always ff @( posedge clk )

{ ip A r, ip B r, ip C r } <=

{ ip n, ip A r, ip B r };

```

# **Helpful SV Primitives**

\$bits( ) - number of bits required to hold value: logic[31:0] foo; // \$bits(foo) = 32 struct happy foo; // \$bits(struct happy) =

'1,'0,'X,'Z – all 1's, all 0's, all X's, etc.

```

logic [63:0] Word; logic [3:0] Byte; // byte = keyword

Word[Byte*8 +: 8]; start at Byte*8; grab 8 bits upwards

Word[Byte*8 -: 8]; start at Byte*8; grab 8 bits downwards

```

# Helpful SV Primitives, Cont.

typedef enum [2:0] { eFetch, eDecode, eExecute, eMemory, eWriteback } state\_e;

```

state e substate r, substate next;

always ff @(posedge clk)

substate r \leq reset? eFetch : substate next:

always comb

unique case (substate r)

eFetch: substate next = eDecode;

eDecode: substate next = eExecute;

eExecute:

unique casez (instr reg)

SW: LW: substate next = eMemory;

default:

substate next = eWriteback;

endcase

eMemory:

unique casez(instruction)

`LW:

substate next = eWriteback;

default: substate next = eFetch;

endcase

eWriteback: substate next = eFetch:

default:

substate next = eFetch;

endcase

```

Breakdown of Verilog case types: http://www.verilogpro.com/verilog-case-casez-casex/

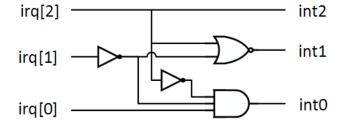

```

always @(irq) begin

{int2, int1, int0} = 3'b000;

casez (irq)

3'b1?? : int2 = 1'b1;

3'b?1? : int1 = 1'b1;

3'b??1 : int0 = 1'b1;

default: {int2, int1, int0} = 3'b000;

endcase end

```

CSE 141L

### That was a lot.

Remember, these slides are meant as a reference.

You are not expected to have internalized all of this in real time in lecture, but to have 'aha' moments when implementing.