CSE 141L: Introduction to Computer Architecture (Lab)

CSE141L - Winter 2022

Meets M/W from 12:00 to 12:50 in CENTR 115.

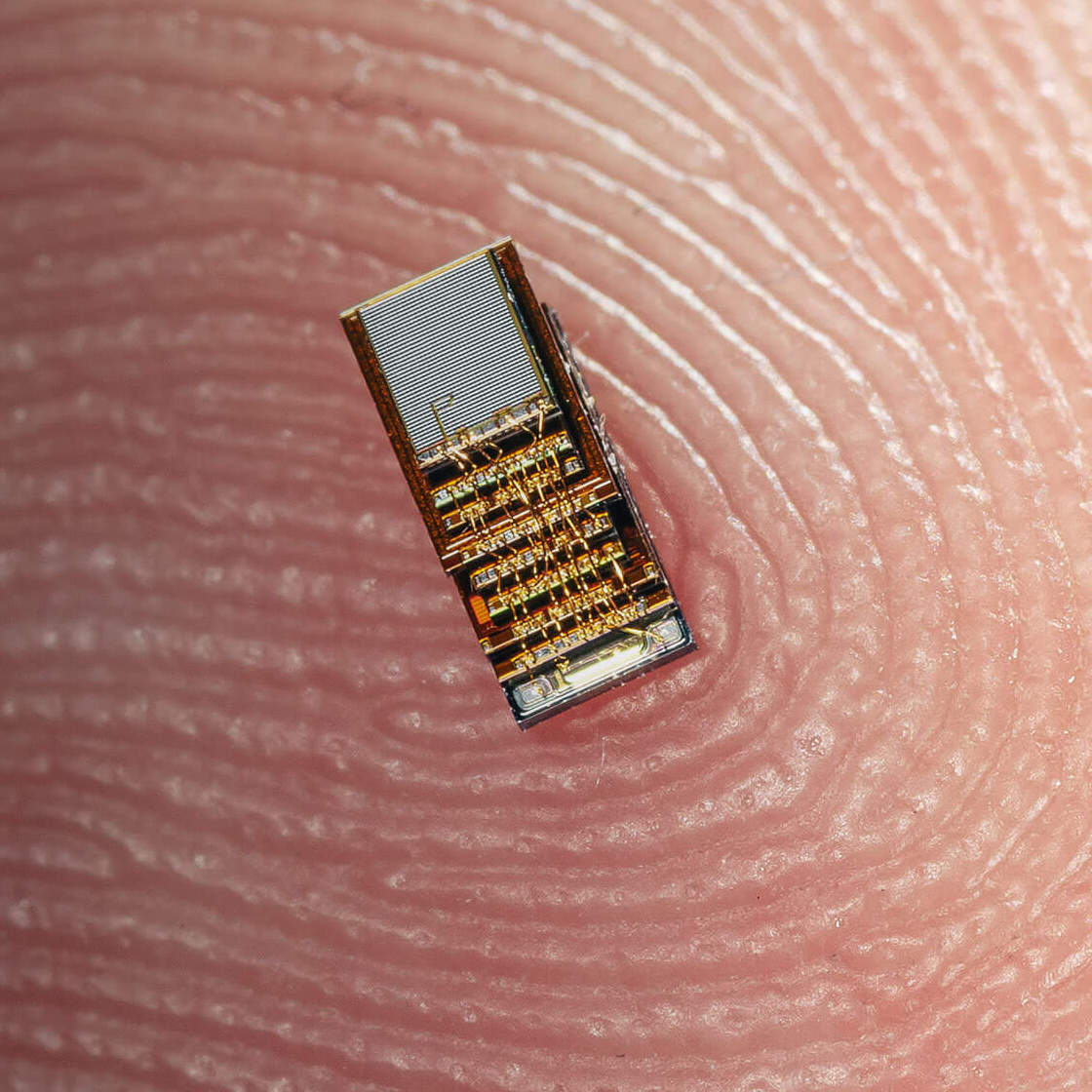

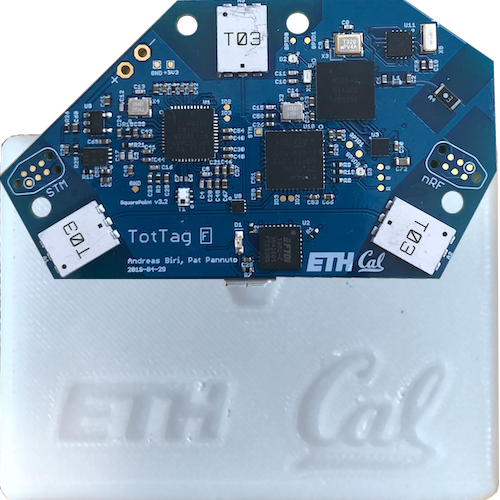

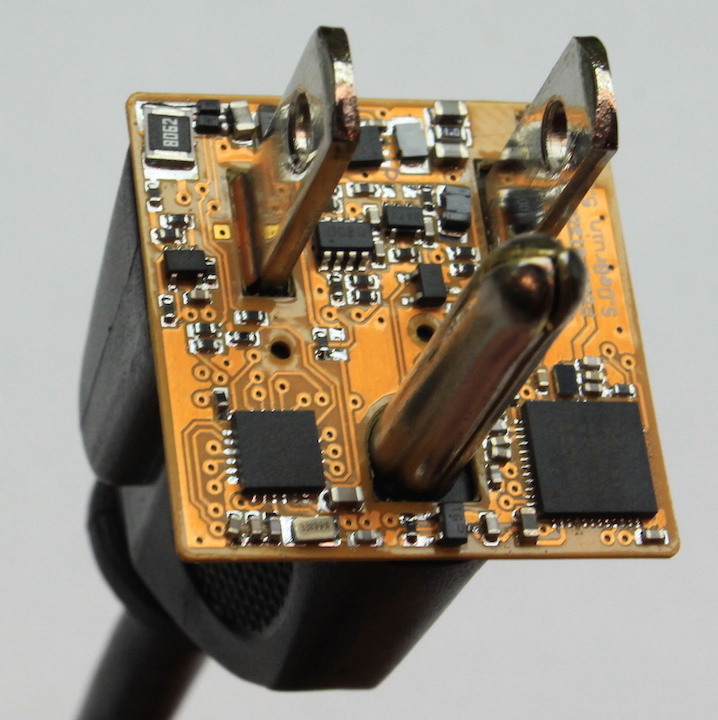

Pat Pannuto is the instructor, and their office is CSE 3202 (right in the corner).

Office hours Wednesday 3:30-4:20pm (via Zoom or

in-person), or always available by appointment (please email / chat after class).

Overview

Hands-on digital design projects aiming to familiarize students with state machines, digital logic implementations, design of processor, control, and memory systems. This is a digital design, simulation, and synthesis project course.

This course is designed to run alongside CSE 141. We expect that you are enrolled in both.

Objectives

By the end of this course, students will be able to:

- Learn correct hardware design practices suitable for FPGA and VLSI digital design.

- Learn how to write Synthesizable Verilog, and to use the tools to turn it into a circuit.

- Design, Implement, and Test your own digital circuits, all the way to an FPGA bitstream.

- Learn about computer architecture in the best way – by doing.

- Learn how programs and algorithms are implemented in hardware.

- Work in a team, building a large, complex system using design principles that apply to both software and hardware.

- Help your classmates and exercise your creativity.

Prerequisites

- CSE141 is a strongly enforced co-requisite. You must either be concurrently enrolled in CSE141 or have previously taken CSE141. It is expected that students take CSE141 and CSE141L in the same term.

- CSE140/140L (Required). This course assumes knowledges of circuits and primitives such as registers and gates, synchronous and combinational logic, state machines, and structures such as muxes and adders. We also assume some familiarity with tools (Quartus, ModelSim, and Verilog generally) from 140/140L.

- CSE110 (Strongly Recommended). 110 gives critical experience in the design, planning, and implementation of a large-scale project. It is strongly encouraged for students to take 110 first, as this course is also a large project but more of the planning and breakdown of work is your own responsibility in 141L.

Syllabus

DISCLAIMER

Due to our unusual circumstances, the details in this syllabus may change (e.g. schedule, grading policy, assignments, etc.). We will update this syllabus in the event of changes as the course progresses.

Instructor

TAs

- Adithya Anand - ananand@ucsd.edu

- Link Lin - yul065@ucsd.edu

- Chavisa Thamjarat - cthamjar@ucsd.edu

- Kanlin Wang - kaw008@ucsd.edu

Schedule

Lectures are M/W from 12:00 to 12:50 US/Pacific, CENTR 115.

Expectations

Course format is two hours of lecture/demo/discussion per week, plus independent work in the CSE basement labs (B250, B260, B270) or at home on own computers. Attendance is strongly recommended, but not required, and all lectures are podcast.

Discussions, Q&A, peer-to-peer instruction, etc. take place on our Piazza website. You are encouraged to post questions, help answer other students' questions, and provide feedback and suggestions to your instruction staff.

What is important to me is that students put forth an honest effort and treat one another, and the instructors, courteously and honestly. Constructive criticism is always welcome.

Academic Integrity

This is a collaborative course, but students are expected to do their own work and to refrain from taking credit for the work of others.

Accommodations for Students with Disabilities

If you have a disability for which you are or may be requesting accommodations, please contact Office for Students with Disabilities. You must have documentation from the Office before accommodations can be granted.

Assignments

Students shall work in teams of one to three members each.

Each group will work over the course of the quarter to design and implement a custom processor.

There are four reports, due at the starts of weeks 4, 6, and 8, plus the final report. Reports shall be submitted on Gradescope.

There is no final exam for this course. The complete processor and its final report are due at the end of the assigned "exam session." This quarter, that is 2:30pm US/Pacific on Wednesday, March 16.

Logistics

Submit reports on Gradescope.

We will use Piazza for Q&A.

Course Resources

- ModelSim (download or use on CSE B250/60/70 lab computers)

- Quartus Prime Lite (download or use on lab computers)

Grading

Each team shall design a specialized RISC processor. These will be tested on instructor-provided testbenches, and final course grades will depend on how well your designs perform against these testbenches and whether your designs can be synthesized into actual digital gate-level logic.

Milestones

There are intermediate deadlines (Milestones 1, 2, and 3). The primary goal of these is to help you ensure that you are on track. They will be evaluated by course staff, but this is primarily for feedback to you for your benefit; generally these will not directly impact your final grade.

An imperfect milestone is okay, but take it as a very serious warning sign that you are behind; it will only get harder to catch up as time progresses. It is far better to submit what you have than to submit nothing.

Each incomplete milestone will lower your course grade by one notch (e.g. , A to A- or A- to B+).

Habitually late submissions may lower your course grade by one notch (e.g. , A to A- or A- to B+).

Agenda

This course meets for one hour twice a week. Loosely speaking, there will be one traditional lecture per week and one interactive demo session showcasing how to use tools or implement ideas covered in lecture.

Update: In accordance with the campus policy, this course will be fully remote for the first two weeks of instruction. We will meet on Zoom. See the Canvas announcement for more details.

| Week | Topic | Readings & Assignments |

|---|---|---|

| Week 1 Jan 3-9 |

|

|

| Week 2 Jan 10-16 |

Microprocessor Types | |

| Week 3 Jan 17-23 |

Microprocessor Implementation | Assembly Language |

| Week 4 Jan 24-30 |

SystemVerilog [slides][pdf] | Milestone 1 DUE Deadline 12:00pm US/Pacific Jan 26 |

| Week 5 Jan 31-Feb 6 |

SystemVerilog Verification [slides][pdf] | SystemVerilog |

| Week 6 Feb 7-13 |

Milestone 2 DUE Deadline 12:00pm US/Pacific Feb 9 |

|

| Week 7 Feb 14-20 |

Debugging

|

|

| Note: To allow for free and open discussion, lectures after this point will not be recorded. | ||

| Week 8 Feb 21-27 |

|

Milestone 3 DUE Deadline 12:00pm US/Pacific Feb 23 |

| Week 9 Feb 28-Mar 6 |

Open Discussions / Q&A | |

| Week 10 Mar 7-13 |

[No Lecture] Good luck on projects! | |

| Week 11 Mar 14-16 |

Final Report DUE Deadline 2:30pm US/Pacific March 16 |

|

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License. Copyright Pat Pannuto, 2022.